LTC7851/LTC7851-1

Quad Output, Multiphase Step-Down Voltage Mode

DC/DC Controller with Accurate Current Sharing

FEATURES

DESCRIPTION

Operates with Power Blocks, DrMOS or External

Gate Drivers and MOSFETs

nn Voltage Mode Control with Accurate Current Sharing

nn ±0.75% 0.6V Voltage Reference

nn Quad Differential Output Voltage Sense Amplifiers

nn Multiphase Capability

nn Phase-Lockable Fixed Frequency 250kHz to 2.25MHz

nn Lossless Current Sensing Using Inductor DCR or

Precision Current Sensing with Sense Resistor or

DrMOS with Integrated Current Sensing

nn V

CC Range: 3V to 5.5V

nn V

OUT Range: 0.6V to VCC – 0.5V

nn Power Good Output Voltage Monitor

nn Output Voltage Tracking Capability with Soft-Start

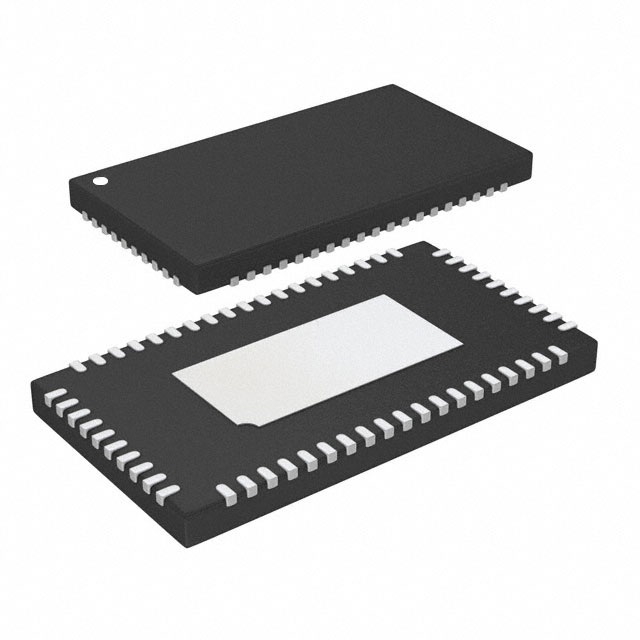

nn Available in 58-Lead 5mm × 9mm QFN Package

The LTC®7851/LTC7851-1 are quad output multiphase synchronous step-down switching regulator controllers that

employ a constant frequency voltage mode architecture.

They maintain excellent current balance between channels

when paralleled with their internal current sharing loop.

Lossless DCR or a low value RSENSE is used for output

current sensing. Multiple LTC7851/LTC7851-1 devices can

be used for high phase count operation.

nn

APPLICATIONS

A very low offset, high bandwidth error amplifier, combined

with remote output voltage sensing, provides excellent

transient response and output regulation. The LTC7851/

LTC7851-1 operates with a VCC supply voltage from 3V to

5.5V and is designed for step-down conversion with VIN

from 3V to 27V* and produces an output voltage from

0.6V to VCC – 0.5V.

The LTC7851-1 is identical to the LTC7851 except it has

a lower current sense amplifier gain, making it ideal for

DrMOS devices with internal current sense.

High Current Distributed Power Systems

nn DSP, FPGA and ASIC Supplies

nn Datacom, Telecom and Computing Systems

nn

All registered trademarks and trademarks are the property of their respective owners. Protected

by U.S. Patents, including 6144194, 5055767.

*See Note 5.

TYPICAL APPLICATION

Dual-Output Converter: 1V/90A and 1.5V/30A with DrMOS

VIN

7V TO 14V

VINSNS

0.25µH

0.25µH

DrMOS

PWM3

3.57k

0.22µF

VOUT2

1.5V/30A

1µF

PINS NOT USED

IN THIS CIRCUIT:

CLKIN

CLKOUT

VSNSP2

VSNSP3

VSNSN2

VSNSN3

PGOOD2

PGOOD3

RUN4

IAVG4

TRACK/SS4

3.57k

0.22µF

ISNS2P

ISNS2N

FB2,3

100k

0.25µH

330µF

x3

+

100µF

x2

3.57k

0.22µF

3.3nF

332Ω

PGOOD1

PWM1

TRACK/SS1

TRACK/SS2

TRACK/SS3

0.25µH

DrMOS

3.57k

0.22µF

ISNS4P

ISNS1P

ISNS4N

ISNS1N

VSNSP4

VSNSP1

VSNSN4

VSNSN1

VSNSOUT4 VSNSOUT1,2,3

6.04k

10k

2.2nF

VCC

100k

PGOOD4

PWM4

RUN1

RUN2

RUN3

DrMOS

15k

10k

DrMOS

LTC7851

ISNS3P

ISNS3N

VCC

VCC

5V

PWM2

100pF

30.9k

42.2k

COMP4

FB4

FREQ

ILIM4

COMP1,2,3

FB1

IAVG1,2,3

ILIM1,2,3

SGND

100µF

x6

+

330µF

x9

VOUT1

1.0V/90A

10k

4.02k

10k

100pF

42.2k

2.2nF

3.3nF

15k

332Ω

100pF

7851 TA01

Rev A

Document Feedback

For more information www.analog.com

1

�LTC7851/LTC7851-1

ABSOLUTE MAXIMUM RATINGS

PIN CONFIGURATION

PGOOD1

PWM2

RUN2

PWM1

RUN1

CLKOUT

CLKIN

TOP VIEW

FREQ

TRACK/SS1

VCC Voltage ............................................... –0.3V to 6.5V

VINSNS Voltage ......................................... –0.3V to 30V

RUN1, RUN2, RUN3,

RUN4 Voltage .............................–0.3V to (VCC+0.3V)

ISNS1P, ISNS1N,

ISNS2P, ISNS2N........................ –0.3V to (VCC + 0.1V)

ISNS3P, ISNS3N,

ISNS4P, ISNS4N........................ –0.3V to (VCC + 0.1V)

All Other Pin Voltages....................–0.3V to (VCC + 0.3V)

Operating Junction Temperature Range.... –40° to 125°C

Storage Temperature Range................... –65°C to 150°C

FB1

(Note 1)

58 57 56 55 54 53 52 51 50 49

COMP1 1

48 ILIM1

VSNSP1 2

47 IAVG1

VSNSN1 3

46 ISNS1P

VSNSOUT1 4

45 ISNS1N

SGND 5

44 ISNS2N

VSNSOUT2 6

43 ISNS2P

VSNSN2 7

42 IAVG2

VSNSP2 8

41 ILIM2

COMP2 9

40 TRACK/SS2

59

SGND

FB2 10

39 VINSNS

VCC 11

38 PGOOD2

FB3 12

37 TRACK/SS3

COMP3 13

36 ILIM3

VSNSP3 14

35 IAVG3

VSNSN3 15

34 ISNS3P

VSNSOUT3 16

33 ISNS3N

VSNSOUT4 17

32 ISNS4N

VSNSN4 18

31 ISNS4P

30 IAVG4

VSNSP4 19

ILIM4

PGOOD3

RUN3

PWM3

PWM4

PGOOD4

RUN4

TRACK/SS4

FB4

COMP4

20 21 22 23 24 25 26 27 28 29

UHH PACKAGE

58-LEAD (5mm × 9mm) PLASTIC QFN

LEAD PITCH 0.4mm

θJA = 49°C/W, θJC = 15.5°C/W

EXPOSED PAD (PIN 59) IS SGND, MUST BE SOLDERED TO PCB

ORDER INFORMATION

LEAD FREE FINISH

TAPE AND REEL

PART MARKING

PACKAGE DESCRIPTION

TEMPERATURE RANGE

LTC7851EUHH#PBF

LTC7851EUHH#TRPBF

7851

58-LEAD (5mm × 9mm) Plastic QFN

–40°C to 125°C

LTC7851IUHH#PBF

LTC7851IUHH#TRPBF

7851

58-LEAD (5mm × 9mm) Plastic QFN

–40°C to 125°C

LTC7851EUHH-1#PBF

LTC7851EUHH-1#TRPBF

78511

58-LEAD (5mm × 9mm) Plastic QFN

–40°C to 125°C

LTC7851IUHH-1#PBF

LTC7851IUHH-1#TRPBF

78511

58-LEAD (5mm × 9mm) Plastic QFN

–40°C to 125°C

Consult ADI Marketing for parts specified with wider operating temperature ranges. *The temperature grade is identified by a label on the shipping container.

Tape and reel specifications. Some packages are available in 500 unit reels through designated sales channels with #TRMPBF suffix.

2

Rev A

For more information www.analog.com

�LTC7851/LTC7851-1

ELECTRICAL CHARACTERISTICS

The l denotes the specifications which apply over the specified operating

junction temperature range, otherwise specifications are at TA = 25°C (Note 2). VCC = 5V, VRUN1,2,3,4 = 5V, VFREQ = VCLKIN = 0V,

VFB = 0.6V, fOSC = 600kHz, unless otherwise specified.

SYMBOL

PARAMETER

CONDITIONS

VINSNS

VIN Sense Range

VCC = 5V (Note 5)

VCC

VCC Voltage Range

VOUT

VOUT Voltage Range

IQ

Input Voltage Supply Current

Normal Operation

Shutdown Mode

UVLO

Limited by ISNSP/N Common Mode

Voltage Range (Note 3)

MIN

l

RUN Input Threshold

VRUN Rising

VRUN Hysteresis

IRUN

RUN Input Pull-Up Current

VRUN = 2.4V

VUVLO

Undervoltage Lockout Threshold

VCC Rising

VCC Hysteresis

ISS

Soft-Start Pin Output Current

VSS = 0V

tSS

Internal Soft-Start Time

VFB

Regulated Feedback Voltage

MAX

V

3

5.5

V

l

0.6

VCC – 0.5

V

60

16

1.95

2.25

250

110

100

mA

µA

mA

2.45

V

mV

1.5

l

100

1.5

2.5

µA

3

3.5

1.5

–20°C to 85°C

–40°C to 125°C

UNITS

27

l

VRUN1,2,3,4 = 5V

VRUN1,2,3,4 = 0V

VCC < VUVLO

VRUN

TYP

3

l

595.5

594

V

mV

µA

ms

600

600

604.5

606

mV

mV

0.05

0.2

%/V

�VFB/�VCC

Regulated Feedback Voltage Line Dependence 3.0V < VCC < 5.5V

ILIMIT

ILIM Pin Output Current

VILIM = 0.8V

18.5

20

21.5

µA

VFB(OV)

PGOOD/VFB Overvoltage Threshold

VFB Falling

VFB Rising

650

645

660

670

mV

mV

VFB(UV)

PGOOD/VFB Undervoltage Threshold

VFB Falling

VFB Rising

VPGOOD(ON)

PGOOD Pull-Down Resistance

IPGOOD(OFF)

PGOOD Leakage Current

VPGOOD = 5V

tPGOOD

PGOOD Delay

VPGOOD High to Low

IFB

FB Pin Input Current

VFB = 600mV

IOUT

COMP Pin Output Current

Sourcing

Sinking

AV(OL)

Open Loop Voltage Gain

SR

Slew Rate

f0dB

COMP Unity-Gain Bandwidth

Power Good

530

540

555

550

mV

mV

15

60

Ω

2

µA

30

µs

Error Amplifier

–100

100

nA

1

4

mA

mA

75

dB

(Note 4)

45

V/µs

(Note 4)

40

MHz

Differential Amplifier

VDA

VSNSP Accuracy

Measured in a Servo Loop with EA in Loop

0°C to 85°C

Measured in a Servo Loop with EA in Loop

–40°C to 125°C

l

594

600

606

mV

592

600

608

mV

IDIFF+

Input Bias Current

VSNSP = 600mV

fOdb

DA Unity-Gain Bandwidth

(Note 4)

–100

40

100

MHz

nA

IOUT(SINK)

Maximum Sinking Current

VSNSOUT = 600mV

100

µA

IOUT(SOURCE)

Maximum Sourcing Current

VSNSOUT = 600mV

500

µA

Rev A

For more information www.analog.com

3

�LTC7851/LTC7851-1

ELECTRICAL CHARACTERISTICS

The l denotes the specifications which apply over the specified operating

junction temperature range, otherwise specifications are at TA = 25°C (Note 2). VCC = 5V, VRUN1,2,3,4 = 5V, VFREQ = VCLKIN = 0V,

VFB = 0.6V, fOSC = 600kHz, unless otherwise specified.

SYMBOL

PARAMETER

CONDITIONS

MIN

TYP

MAX

UNITS

Current Sense Amplifier

VISENSE(MAX)

Maximum Differential Current Sense Voltage

(VISNSP – VISNSN)

LTC7851

50

mV

LTC7851-1

150

mV

AV(ISENSE)

Voltage Gain

LTC7851

VCM(ISENSE)

Input Common Mode Range

IISENSE

SENSE Pin Input Current

VCM = 1.5V

VIAVG

Zero Current IAVG Pin Voltage

VISNSP = VISNSN

VOS

Current Sense Input Referred Offset

LTC7851

l

–1

1

mV

LTC7851-1

l

–3

3

mV

l

l

520

0.85

680

1.15

kHz

MHz

20

LTC7851-1

V/V

4

–0.3

V/V

VCC – 0.5

100

V

nA

500

mV

Oscillator and Phase-Locked Loop

fOSC

Oscillator Frequency

VCLKIN = 0V

VFREQ = 0V

VFREQ = 5V

VCLKIN = 5V

RFREQ < 24.9k

RFREQ = 30.9k

RFREQ = 36.5k

RFREQ = 48.7k

RFREQ = 64.9k

RFREQ = 82.5k

RFREQ = 88.7k

600

1

180

370

570

970

1.4

1.9

2.1

Maximum Frequency

kHz

kHz

kHz

kHz

MHz

MHz

MHz

3

MHz

Minimum Frequency

MHz

21.5

µA

IFREQ

FREQ Pin Output Current

VFREQ = 0.8V

18.5

tCLKIN(HI)

CLKIN Pulse Width High

VCLKIN = 0V to 5V

100

ns

tCLKIN(LO)

CLKIN Pulse Width Low

VCLKIN = 0V to 5V

100

ns

RCLKIN

CLKIN Pull Up Resistance

20

kΩ

VCLKIN

CLKIN Input Threshold

VCLKIN Falling

VCLKIN Rising

0.8

2

V

V

VFREQ

FREQ Input Threshold

VCLKIN = 0V

VFREQ Falling

VFREQ Rising

1.5

2.5

V

V

VOL(CLKOUT)

CLKOUT Low Output Voltage

ILOAD = –500µA

0.2

V

VOH(CLKOUT)

CLKOUT High Output Voltage

ILOAD = 500µA

VCC – 0.2

θ2 – θ1

θ3 – θ1

θ4 – θ1

θCLKOUT – θ1

20

0.25

V

Channel 2 to Channel 1 Phase Relationship

180

Deg

Channel 3 to Channel 1 Phase Relationship

90

Deg

Channel 4 to Channel 1 Phase Relationship

270

Deg

CLKOUT to Channel 1 Phase Relationship

45

Deg

PWM Output

PWM

PWM Output High Voltage

ILOAD = 500µA

l

PWM Output Low Voltage

ILOAD = –500µA

l

VCC – 0.5

V

PWM Output Current in Hi-Z State

PWM Maximum Duty Cycle

4

91.5

0.5

V

±5

µA

%

Rev A

For more information www.analog.com

�LTC7851/LTC7851-1

ELECTRICAL CHARACTERISTICS

Note 1: Stresses beyond those listed under Absolute Maximum Ratings

may cause permanent damage to the device. Exposure to any Absolute

Maximum Rating condition for extended periods may affect device

reliability and lifetime.

Note 2:� The LTC7851/LTC7851-1 are tested under pulsed load conditions

such that TJ ≈ TA. The LTC7851E/LTC7851E-1 are guaranteed to meet

performance specifications from 0°C to 85°C. Specifications over the

–40°C to 125°C operating junction temperature range are assured by

design, characterization and correlation with statistical process controls.

The LTC7851I/LTC7851I-1 are guaranteed over the –40°C to 125°C

operating junction temperature range. Note that the maximum ambient

temperature consistent with these specifications is determined by specific

operating conditions in conjunction with board layout, the rated package

thermal impedance and other environmental factors. TJ is calculated from

the ambient temperature TA and power dissipation PD according to the

following formula:

TJ = TA + (PD • 49˚C/W)

Note 3: The maximum VOUT range is limited by the current sense pins

(ISNSP/ISNSN) common mode voltage range. See the Current Sensing in

the Applications Information section.

Note 4: Guaranteed by design.

Note 5: The Absolute Maximum Voltage Rating for the VINSNS voltage

limits the Maximum VIN Voltage. For operation with a VIN range higher

than 27V, the VINSNS pin must be connected through a resistor divider

from VIN to limit the maximum VINSNS voltage to less than 27V.

TYPICAL PERFORMANCE CHARACTERISTICS

Load Step Transient Response

(Single Phase Using

FDMF5820DC DrMOS)

Load Step Transient Response

(2-Phase Using FDMF58200C

DrMOS)

ILOAD

25A/DIV

ILOAD

20A/DIV

0A TO 15A TO 0A

IL1

10A/DIV

IL

20A/DIV

VOUT

AC-COUPLED

50mV/DIV

IL2

10A/DIV

VIN = 12V

VOUT = 1.8V

fSW = 400kHz

VOUT

AC-COUPLED

50mV/DIV

7851 G01

50µs/DIV

7851 G02

20µs/DIV

VIN = 12V

VOUT = 1.2V

fSW = 400kHz

ILOAD = 10A TO 30A TO 10A

Load Step Transient Response

(4-Phase Using FDMF5820DC

DrMOS)

Load Step Transient Response

(3-Phase Using FDMF5820DC

DrMOS)

ILOAD

50A/DIV

0A TO 50A TO 0A

IL1

20A/DIV

IL2

20A/DIV

VOUT

AC-COUPLED

20mV/DIV

IL3

20A/DIV

VIN = 12V

VOUT = 1.2V

fSW = 400kHz

VOUT

AC-COUPLED

50mV/DIV

40µs/DIV

VIN = 12V

VOUT = 1.2V

fSW = 400kHz

ILOAD = 0A TO 38A TO 0A

7851 G03

40µs/DIV

7851 G04

Rev A

For more information www.analog.com

5

�LTC7851/LTC7851-1

TYPICAL PERFORMANCE CHARACTERISTICS

Line Step Transient Response

(2-Phase Using FDMF5820DC

DrMOS)

EFFICIENCY (%)

IL1

10A/DIV

IL2

10A/DIV

VOUT

50mV/DIV

AC-COUPLED

VOUT = 1.2V

ILOAD = 15A

100

100

90

90

80

80

70

70

EFFICIENCY (%)

VIN

10V/DIV

7V TO 14V

60

50

40

30

20

7851 G05

20µs/DIV

Efficiency vs Load Current

(4-Phase Using D12S1R8130A

Power Block)

Efficiency vs Load Current

(2-Phase Using D12S1R8130A

Power Block)

fSW = 400kHz

VIN = 12V

VOUT = 1.2V

10

0

0

10

20

30

40

50

LOAD CURRENT (A)

60

70

60

50

40

30

10

0

3681 G06

Feedback Voltage VFB vs

Temperature

602

REGULATED VFB VOLTAGE (mV)

REGULATED VFB VOLTAGE (mV)

602

601

600

599

598

–50

–25

0

25

50

75

TEMPERATURE (°C)

100

125

0

20

40

60

80 100

LOAD CURRENT (A)

120

140

3681 G07

Start-Up Response (2-Phase

Using FDMF5820DC DrMOS)

Regulated VFB vs Supply Voltage

RUN

5V/DIV

601

IL1

20A/DIV

IL2

20A/DIV

600

VOUT

1V/DIV

599

CSS = 0.1µF

5ms/DIV

598

3

3.5

4

4.5

SUPPLY VOLTAGE (V)

5

7851 G08

7851 G10

VIN = 12V

VOUT = 1.2V

RLOAD = 0.037Ω

fSW = 400kHz

5.5

7851 G09

Start-Up Response

(4-Phase Using D12S1R8130A

Power Block)

Start-Up Response (3-Phase

Using FDMF5820DC DrMOS)

RUN

5V/DIV

IL1

20A/DIV

IL2

20A/DIV

IL3

20A/DIV

ILOAD

50A/DIV

VOUT

1V/DIV

VOUT

1V/DIV

Coincident Tracking (Single Phase

Using FDMF5820DC DrMOS)

VIN = 12V

VOUT = 1.8V

RUN

4V/DIV

TRACK/SS

500mV/DIV

INTERNAL SOFT-START

RLOAD = 27mΩ

VIN = 12V

VOUT = 1.2V

6

fSW = 400kHz

VIN = 12V

VOUT = 1.2V

Airflow ≈ 400LFM

20

400µs/DIV

VOUT

1V/DIV

RLOAD = 0.01Ω

fSW = 400kHz

INTERNAL

SOFT–START

7851 G11

VIN = 12V

VOUT = 1.2V

RLOAD = 0.017Ω

fSW = 400kHz

500µs/DIV

7851 G12

2ms/DIV

7851 G13

Rev A

For more information www.analog.com

�LTC7851/LTC7851-1

TYPICAL PERFORMANCE CHARACTERISTICS

Initial 7-Cycle Nonsynchronous

Start-Up (Single Phase Using

FDMF5820DC DrMOS)

Start-Up Response Into a 300mV

Prebiased Output (Single Phase

Using FDMF5820DC DrMOS)

IL

5A/DIV

Start-Up Into a Short (2-Phase

Using FDMF5820DC DrMOS)

TRACK/SS

1V/DIV

IL

10A/DIV

PWM

5V/DIV

IL1

50A/DIV

PWM

5V/DIV

VOUT

500mV/DIV

VIN = 12V

VOUT = 1.8V

10µs/DIV

IL2

50A/DIV

VOUT

1V/DIV

VIN = 12V

VOUT = 1.8V

7851 G14

IL1

20A/DIV

IL2

20A/DIV

VIN = 12V

VOUT = 1.2V

7851 G17

50µs/DIV

Oscillator Frequency vs RFREQ

Frequency < 1MHz

1050

1000

950

900

850

800

750

700

650

600

550

500

450

400

350

300

250

200

150

Oscillator Frequency vs RFREQ

Frequency ≥ 1MHz

OSCILLATOR FREQUENCY (kHz)

VOUT

1V/DIV

OSCILLATOR FREQUENCY (kHz)

TRACK/SS1

2V/DIV

24 27 30 33 36 39 42 45 48 51 54

RFREQ (kΩ)

2200

2100

2000

1900

1800

1700

1600

1500

1400

1300

1200

1100

1000

900

45

50

3681 G18

LTC7851-1 Overcurrent Threshold

vs Temperature

20.8

80

70

60

ILIM = 680mV

50

30

–50

–25

0

25

50

75

TEMPERATURE (°C)

100

125

7851 G20

65 70 75

RFREQ (kΩ)

80

85

90

3681 G19

20.4

20.4

20.2

20

19.8

19.4

–50

60

FREQ Pin Current vs Temperature

20.2

20

19.8

19.6

19.4

19.6

40

55

20.6

20.6

ILIM = 860mV

90

ILIM Pin Current vs Temperature

FREQ PIN CURRENT (µA)

100

ILIM PIN CURRENT (µA)

CURRENT SENSE VOLTAGE (mV)

110

7851 G16

200µs/DIV

VIN = 12V

CTRACK/SS = 2200pF

7851 G15

200µs/DIV

128-Cycle Overcurrent Counter

(2-Phase Using FDMF5820DC DrMOS)

VOUT

50mV/DIV

–25

0

25

50

75

TEMPERATURE (°C)

100

125

7851 G21

19.2

–50

–25

0

25

50

75

TEMPERATURE (°C)

100

125

7851 G22

Rev A

For more information www.analog.com

7

�LTC7851/LTC7851-1

TYPICAL PERFORMANCE CHARACTERISTICS

1MHz Preset Frequency vs

Temperature

1000

595

990

590

585

580

575

570

565

–50

–25

0

25

50

75

TEMPERATURE (°C)

100

980

970

960

–25

0

25

50

75

TEMPERATURE (°C)

100

Shutdown Quiescent Current vs

Supply Voltage

60

–50

125

0

25

50

75

TEMPERATURE (°C)

100

125

RUN Threshold vs Temperature

2.5

65

2.4

40

30

20

2.3

RUN PIN VOLTAGE (V)

SHUTDOWN CURRENT (µA)

50

60

55

RISING

2.2

2.1

FALLING

2.0

1.9

1.8

1.7

10

1.6

0

1

2

3

4

SUPPLY VOLTAGE (V)

5

50

–50

6

7851 G26

–25

0

25

50

75

TEMPERATURE (°C)

100

1.5

–50

125

2.0

0

2.9

1.2

1.0

–50

TRACK/SS PIN CURRENT (µA)

3.0

TRACK/SS PIN CURRENT (µA)

0.5

1.4

–0.5

–1.0

–1.5

–2.0

–2.5

–25

0

25

50

75

TEMPERATURE (°C)

100

125

7851 G29

100

–3.0

125

TRACK/SS Pull-Up Current vs

Temperature

2.2

1.6

0

25

50

75

TEMPERATURE (°C)

7851 G28

TRACK/SS Current vs TRACK/SS

Voltage

1.8

–25

7851 G27

RUN Pull-Up Current vs

Temperature

8

–25

7851 G25

60

SHUTDOWN CURRENT (µA)

65

Shutdown Quiescent Current vs

Temperature

70

RUN PIN CURRENT (µA)

70

7851 G24

7851 G23

0

VIN = VCC = 5V

RUN1 = RUN2 = RUN3 = RUN4 = 5V

950

940

–50

125

Quiescent Current vs Temperature

75

QUIESCENT CURRENT (mA)

600

OSCILLATOR FREQUENCY (kHz)

OSCILLATOR FREQUENCY (kHz)

600kHz Preset Frequency vs

Temperature

2.8

2.7

2.6

2.5

2.4

2.3

0

1

2

3

4

TRACK/SS PIN VOLTAGE (V)

5

7851 G30

2.2

–50

–25

0

25

50

75

TEMPERATURE (°C)

100

125

7851 G31

Rev A

For more information www.analog.com

�LTC7851/LTC7851-1

PIN FUNCTIONS

COMP1 (Pin 1), COMP2 (Pin 9), COMP3 (Pin 13), COMP4

(Pin 20): Error Amplifier Outputs. PWM duty cycle increases with this control voltage. The error amplifiers in

the LTC7851/LTC7851-1 are true operational amplifiers

with low output impedance. As a result, the outputs of

two active error amplifiers cannot be directly connected

together! For multiphase operation, connecting the FB pin

on an error amplifier to VCC will three-state the output of

that amplifier. Multiphase operation can then be achieved

by connecting all of the COMP pins together and using

one channel as the master and all others as slaves. When

the RUN pin is low, the respective COMP pin is actively

pulled down to ground.

VSNSP1 (Pin 2), VSNSP2 (Pin 8), VSNSP3 (Pin 14),

VSNSP4 (Pin 19): Differential Sense Amplifier Noninverting

Input. Connect this pin to the midpoint of the feedback

resistive divider between the positive and negative output

capacitor terminals.

VSNSN1 (Pin 3), VSNSN2 (Pin 7), VSNSN3 (Pin 15),

VSNSN4 (Pin 18): Differential Sense Amplifier Inverting

Input. Connect this pin to sense ground at the output load.

If the differential sense amplifier is not used, connect this

pin to local ground. Float this pin when the channel is a

slave channel.

VSNSOUT1 (Pin 4), VSNSOUT2 (Pin 6), VSNSOUT3

(Pin 16), VSNSOUT4 (Pin 17): Differential Amplifier Output.

Connect to the corresponding FB pin with a compensation

network for remote VOUT sensing. PolyPhase control is also

implemented in part by connecting all slave VSNSOUT pins

to the master VSNSOUT output. Only the master phase’s

differential amplifier contributes information to this output.

SGND (Pin 5, Exposed Pad Pin 59): Signal Ground. All

soft-start, small-signal and compensation components

should return to SGND. The exposed pad must be soldered

to PCB ground for rated thermal performance.

FB1 (Pin 58), FB2 (Pin 10), FB3 (Pin 12), FB4 (Pin 21):

Error Amplifier Inverting Input. Connect to the corresponding VSNSOUT pin with a compensation network for remote

VOUT sensing. Connecting the FB to VCC disables the differential and error amplifiers of the respective channel,

and will three-state the amplifier outputs.

VCC (Pin 11): Chip Supply Voltage. Bypass this pin to GND

with a capacitor (0.1μF to 1μF ceramic) in close proximity

to the chip.

TRACK/SS1 (Pin 57), TRACK/SS2 (Pin 40), TRACK/SS3

(Pin 37), TRACK/SS4 (Pin 22): Combined Soft-Start and

Tracking Inputs. For soft-start operation, connecting a

capacitor from this pin to ground will control the voltage

ramp at the output of the power supply. An internal 2.5μA

current source will charge the capacitor and thereby control

an extra input on the reference side of the error amplifier.

For coincident tracking of both outputs at start-up, a resistor divider with values equal to those connected to the

secondary VSNSP pin from the secondary output should

be used to connect the secondary track input from the

primary output. This pin is internally clamped to 2V, and

is used to communicate over current events in a masterslave configuration.

RUN1 (Pin 53), RUN2 (Pin 51), RUN3 (Pin 27), RUN4 (Pin

23): Run Control Inputs. A voltage above 2.25V on either

pin turns on the IC. However, forcing a RUN pin below 2V

causes the IC to shut down that particular channel. There

are 1.5μA pull-up currents for these pins.

PWM1 (Pin 52), PWM2 (Pin 50), PWM3 (Pin 26), PWM4

(Pin 24): (Top) Gate Signal Output. This signal goes to

the PWM or top gate input of the external gate driver or

integrated driver MOSFET. This is a three-state compatible output. In three-state, the voltage of this pin will be

determined by the external resistor divider.

PGOOD1 (Pin 49), PGOOD2 (Pin 38), PGOOD3 (Pin 28),

PGOOD4 (Pin 25): Power Good Indicator Output for Each

Channel. Open-drain logic out that is pulled to SGND when

either channel output exceeds a ±10% regulation window,

after the internal 30μs power bad mask timer expires.

ILIM1 (Pin 48), ILIM2 (Pin 41), ILIM3 (Pin 36), ILIM4 (Pin

29): Current Comparator Sense Voltage Limit Selection

Pin. Connect a resistor from this pin to SGND. This pin

sources 20μA when the channel is a master channel.

This pin does not source current when the channel is a

slave channel. The resultant voltage sets the threshold for

overcurrent protection. For multiphase operation, all ILIM

pins are tied together and only master channel's ILIM pin

sources 20μA.

Rev A

For more information www.analog.com

9

�LTC7851/LTC7851-1

PIN FUNCTIONS

IAVG1 (Pin 47), IAVG2 (Pin 42), IAVG3 (Pin 35), IAVG4 (Pin

30): Average Current Monitor Pin. A capacitor tied to

ground from the IAVG pin stores a voltage proportional to

the instantaneous average current of the master channel.

When the average current is zero, the IAVG pin voltage is

500mV. PolyPhase control is also implemented in part

by connecting all slave IAVG pins together to the master

IAVG output. The total capacitance on the IAVG bus should

range from 47pF to 220pF, inclusive, with the typical value

being 100pF. Only the master phase contributes information to this average through an internal resistor in current

sharing mode.

ISNS1P (Pin 46), ISNS2P (Pin 43), ISNS3P (Pin 34),

ISNS4P (Pin 31): Current Sense Amplifier(+) Input. The (+)

input to the current sense amplifier is normally connected

to the midpoint of the inductor’s parallel RC sense circuit

or to the node between the inductor and sense resistor if

using a discrete sense resistor.

ISNS1N (Pin 45), ISNS2N (Pin 44), ISNS3N (Pin 33),

ISNS4N (Pin 32): Current Sense Amplifier(–) Input. The

(–) input to the current amplifier is normally connected

to the respective VOUT at the inductor.

CLKOUT (Pin 54): Digital Output used for Daisychaining

Multiple LTC7851/LTC7851-1 ICs in Multiphase Systems.

When all RUN pins are driven low, the CLKOUT pin is actively pulled up to VCC. Signal swing is from VCC to ground.

CLKIN (Pin 55): External Clock Synchronization Input.

Applying an external clock between 250kHz to 2.25MHz

will cause the switching frequency to synchronize to the

clock. CLKIN is pulled high to VCC by a 20k internal resistor. The rising edge of the CLKIN input waveform will align

with the rising edge of PWM1 in closed-loop operation. If

CLKIN is high or floating, a resistor from the FREQ pin to

SGND sets the switching frequency. If CLKIN is low, the

FREQ pin logic state selects an internal 600kHz or 1MHz

preset frequency.

FREQ (Pin 56): Frequency Set/Select Pin. This pin sources

20μA current. If CLKIN is high or floating, then a resistor

between this pin and SGND sets the switching frequency. If

CLKIN is low, the logic state of this pin selects an internal

600kHz or 1MHz preset frequency.

VINSNS (Pin 39): VIN Sense Pin. Connects to the VIN

power supply to provide line feedforward compensation.

A change in VIN immediately modulates the input to the

PWM comparator and changes the pulse width in an inversely proportional manner, thus bypassing the feedback

loop and providing excellent transient line regulation. An

external lowpass filter can be added to this pin to prevent

noisy signals from affecting the loop gain.

10

Rev A

For more information www.analog.com

�LTC7851/LTC7851-1

BLOCK DIAGRAM

4

2

3

6

8

7

1

57

58

(Only CH1 and CH2 Are Shown)

VSNSOUT1

53

11

5

VCC

SGND

VCC

VSNSP1

1.5µA

100k

1.5µA

PGOOD2

VSNSOUT1 VSNSOUT2

VCC

VSNSP2

COMP1

38

PGOOD1

PGOOD

VCC

VSNSOUT2

VSNSN2

49

RUN2

100k

DA

VSNSN1

51

RUN1

DA

BG/BIAS

REF

TRACK/SS1

+

FB1

–

+

SD/UVLO

OC1 OC2

+

EA1

OV1 OV2

PWM1

52

NOC1

40

10

9

REF

TRACK/SS2

+

FB2

–

+

LOGIC

+

EA2

VFB1

ILIM1

VFB2

ILIM2

COMP2

MASTER/SLAVE/

INDEPENDENT

45

ISNS1P

ISNS1N

44

ISNS2P

ISNS2N

50

39

20µA

+

AV(ISENSE)

–

OC1

VCC

NOC1

20µA

S

43

VINSNS

RAMP/SLOPE/

FEEDFORWARD

VCC

S

46

PWM2

NOC2

+

VCC

AV(ISENSE)

20µA

–

OC2

PLL/VCO

NOC2

IAVG1

47

IAVG2

42

ILIM2

41

ILIM1

48

FREQ

56

CLKOUT CLKIN

54

55

7851BD

Rev A

For more information www.analog.com

11

�LTC7851/LTC7851-1

OPERATION (Refer to Block Diagram)

Main Control Architecture

The LTC7851/LTC7851-1 are quad-channel/quad-phase,

constant frequency, voltage mode controllers for DC/DC

step-down applications. They are designed to be used

in a synchronous switching architecture with external

integrated-driver MOSFETs (DrMOS), power blocks, or

external drivers and N-channel MOSFETs using single wire

three-state PWM interfaces. The LTC7851-1 is particularly

suited for applications using power stages with integrated

current sense signals. The controllers allow the use of

sense resistors or lossless inductor DCR current sensing to maintain current balance between phases and to

provide overcurrent protection. The operating frequency

is selectable from 250kHz to 2.25MHz. To multiply the

effective switching frequency, multiphase operation can

be extended to 2, 3, 4, 8, or higher phases by paralleling

additional controllers. In single phase operation, each

channel can be used as an independent output, i.e. one

single LTC7851/LTC7851-1 can provide four outputs.

Unlike a conventional differential amplifier, in which the

output is connected directly to the diffamp sensing pins,

the output voltage is resistively divided externally to create a feedback voltage for the controller (see Figure 3,

and Figure 4). Connect VSNSP of the unity-gain internal

differential amplifier, DA, to the center tap of the feedback

divider across the output load, and VSNSN to the load

ground. The output of the differential amplifier VSNSOUT

produces a signal equal to the differential voltage sensed

across VSNSP and VSNSN. This scheme overcomes any

ground offsets between local ground and remote output

ground and common mode voltage variations, resulting in

a more accurate output voltage.

In the main voltage mode control loop, the error amplifier output (COMP) directly controls the converter duty

cycle in order to drive the FB pin to 0.6V in steady state.

Dynamic changes in output load current can perturb the

output voltage. When the output is below regulation,

COMP rises, increasing the duty cycle. If the output rises

above regulation, COMP will decrease, decreasing the

duty cycle. As the output approaches regulation, COMP

will settle to the steady-state value representing the stepdown conversion ratio.

12

In normal operation, the PWM latch is set high at the beginning of the clock cycle (assuming COMP > 0.5V). When

the (line feedforward compensated) PWM ramp exceeds

the COMP voltage, the comparator trips and resets the

PWM latch. If COMP is less than 0.5V at the beginning

of the clock cycle, as in the case of an overvoltage at the

outputs, the PWM pin remains low throughout the entire

cycle. When the PWM pin goes high, it has a minimum

on-time of approximately 20ns and a minimum off-time

of approximately one-twelfth the switching period.

Current Sharing

In multiphase operation, the LTC7851/LTC7851-1 also

incorporate an auxiliary current sharing loop. Inductor

current is sampled each cycle. The master’s current sense

amplifier output is averaged at the IAVG pin. A small capacitor connected from IAVG to GND (typically 100pF) stores a

voltage corresponding to the instantaneous average current

of the master. Master phase's and slave phase's IAVG pins

must be connected together. Each slave phase integrates

the difference between its current and the master’s.

Within each phase the integrator output is proportionally

summed with the system error amplifier voltage (COMP),

adjusting that phase’s duty cycle to equalize the currents.

When multiple ICs are daisy chained, the IAVG pins must

be connected together. Figure 1 shows a transient load

step with current sharing in a 3-phase system.

IL1 (L= 0.47µH)

10A/DIV

IL2 (L= 0.25µH)

10A/DIV

IL3 (L= 0.47µH)

10A/DIV

VOUT

100mV/DIV

AC-COUPLED

7851 F01

VIN = 12V

VOUT = 1V

50µs/DIV

ILOAD STEP = 0A TO 30A TO 0A

fSW = 500kHz EXTERNAL CLOCK

Figure 1. Mismatched Inductor Load Step Transient Response

Overcurrent Protection

The current sense amplifier outputs also connect to overcurrent (OC) comparators that provide fault protection in

the case of an output short. When an OC fault is detected

Rev A

For more information www.analog.com

�LTC7851/LTC7851-1

OPERATION (Refer to Block Diagram)

for 128 consecutive clock cycles, the controller threestates the PWM output, resets the soft-start capacitor,

and waits for 32768 clock cycles before attempting to

start up again. The 128 consecutive clock cycle counter

has a 7-cycle hysteresis window, after which it will reset.

The LTC7851/LTC7851-1 also provide negative OC (NOC)

protection by preventing turn-on of the bottom MOSFET

during a negative OC fault condition. In this condition, the

bottom MOSFET will be turned on for 40ns every eight

cycles to allow the driver IC to recharge its topside gate

drive capacitor. The negative OC threshold is equal to –3/4

the positive OC threshold. See the Applications Information section for guidelines on setting these thresholds.

Excellent Transient Response

The LTC7851/LTC7851-1 error amplifiers are true

operational amplifiers, meaning that they have high

bandwidth, high DC gain, low offset and low output

impedance. Their bandwidth, when combined with high

switching frequencies and low-value inductors, allows

the compensation network to be optimized for very high

control loop crossover frequencies and excellent transient

response. The 600mV internal reference allows regulated

output voltages as low as 600mV without external levelshifting amplifiers.

Line Feedforward Compensation

The LTC7851/LTC7851-1 achieve outstanding line transient

response using a feedforward correction scheme which

instantaneously adjusts the duty cycle to compensate for

changes in input voltage, significantly reducing output

overshoot and undershoot. It has the added advantage

of making the DC loop gain independent of input voltage.

Figure 2 shows how large transient steps at the input have

little effect on the output voltage.

VIN

10V/DIV

7V TO 14V

IL1

10A/DIV

IL2

10A/DIV

VOUT

50mV/DIV

AC-COUPLED

VOUT = 1.2V

ILOAD = 15A

20µs/DIV

7851 F02

Figure 2. Line Step Transient Response

Remote Sense Differential Amplifier

The LTC7851/LTC7851-1 include four low offset, unity

gain, high bandwidth differential amplifiers for differential

output sensing. Output voltage accuracy is significantly

improved by removing board interconnection losses from

the total error budget.

The noninverting input of the differential amplifier is connected to the midpoint of the feedback resistive divider

between the positive and negative output capacitor terminals. The VSNSOUT is connected to the FB pin and the

amplifier will attempt to regulate this voltage to 0.6V. The

amplifier is configured for unity gain, meaning that the

differential voltage between VSNSP and VSNSN is translated

to VSNSOUT, relative to SGND.

Shutdown Control Using the RUN Pins

Each channel of the LTC7851/LTC7851-1 can be independently enabled using its own RUN pin. When all RUN pins

are driven low, all internal circuitry, including the internal

reference and oscillator, are completely shut down. When

the RUN pin is low, the respective COMP pin is actively

pulled down to ground. In a multiphase operation when

the COMP pins are tied together, the COMP pin is held

low until all the RUN pins are enabled. This ensures a

synchronized start-up of all the channels. A 1.5μA pull-up

current is provided for each RUN pin internally. The RUN

pins remain high impedance up to VCC.

Undervoltage Lockout

To prevent operation of the power supply below safe input

voltage levels, all channels are disabled when VCC is below

Rev A

For more information www.analog.com

13

�LTC7851/LTC7851-1

OPERATION (Refer to Block Diagram)

the undervoltage lockout (UVLO) threshold (2.9V falling, 3V

rising). If a RUN pin is driven high, the LTC7851/LTC7851-1

will start up the reference to detect when VCC rises above

the UVLO threshold, and enable the appropriate channel.

Overvoltage Protection

If the output voltage rises to more than 10% above the

set regulation value, which is reflected as a VSNSOUT

voltage of 0.66V or above, the LTC7851/LTC7851-1 will

force the PWM output low to turn on the bottom MOSFET

and discharge the output. Normal operation resumes

once the output is back within the regulation window.

However, if the reverse current flowing from VOUT back

through the bottom power MOSFET to PGND is greater

than 3/4 the positive OC threshold, the NOC comparator

trips and shuts off the bottom power MOSFET to protect

it from being destroyed. This scenario can happen when

the LTC7851/LTC7851-1 try to start into a precharged

load higher than the OV threshold. As a result, the bottom

switch turns on until the amount of reverse current trips

the NOC comparator threshold.

Nonsynchronous Start-Up and Prebiased Output

The LTC7851/LTC7851-1 will start up with seven cycles

of nonsynchronous operation before switching over to a

forced continuous mode of operation. The PWM output will

be in a three-state condition until start-up. The controller

will start the seven nonsynchronous cycles if it is not in

an overcurrent or prebiased condition, and if the COMP

pin voltage is higher than 500mV, or if the TRACK/SS

pin voltage is higher than 900mV. During the seven

nonsynchronous cycles the PWM latch is set high at the

beginning of the clock cycle, if COMP > 0.5V, causing the

PWM output to transition from three-state to VCC. The latch

is reset when the PWM ramp exceeds the COMP voltage,

causing the PWM output to transition from VCC to threestate followed immediately by a 20ns three-state to ground

pulse. The 7-cycle nonsynchronous mode of operation is

enabled at initial start-up and also during a restart from

a fault condition. In multiphase operation, where all the

TRACK/SS pins should be connected together, only an

overcurrent event on the master channel will discharge the

14

soft-start capacitor. After 32768 cycles, it will synchronize

the restart of all channels in to the nonsynchronous mode

of operation.

The LTC7851/LTC7851-1 can safely start-up into a prebiased output without discharging the output capacitors. A

prebias is detected when the FB pin voltage is higher than the

TRACK/SS or the internal soft-start voltage. A prebiased

condition will force the COMP pin to be held low, and

will three-state the PWM output. The prebiased condition

is cleared when the TRACK/SS or the internal soft-start

voltage is higher than the FB pin voltage or 900mV, whichever is lower. If the output prebias is higher than the OV

threshold then the PWM output will be low, which will pull

the output back in to the regulation window.

Internal Soft-Start

By default, the start-up of each channel’s output voltage

is normally controlled by an internal soft-start ramp. The

internal soft-start ramp represents a noninverting input to

the error amplifier. The FB pin is regulated to the lower of

the error amplifier’s three noninverting inputs (the internal

soft-start ramp for that channel, the TRACK/SS pin or the

internal 600mV reference). As the ramp voltage rises from

0V to 0.6V over approximately 2ms, the output voltage

rises smoothly from its prebiased value to its final set value.

Soft-Start and Tracking Using TRACK/SS Pin

The user can connect an external capacitor greater than

10nF to the TRACK/SS pin for the relevant channel to

increase the soft-start ramp time beyond the internally

set default. The TRACK/SS pin represents a noninverting

input to the error amplifier and behaves identically to the

internal ramp described in the previous section. An internal

2.5µA current source charges the capacitor, creating a

voltage ramp on the TRACK/SS pin. The TRACK/SS pin

is internally clamped to 2V. As the TRACK/SS pin voltage

rises from 0V to 0.6V, the output voltage rises smoothly

from 0V to its final value in:

CSS (µF ) • 0.6V

seconds

2.5µA

Rev A

For more information www.analog.com

�LTC7851/LTC7851-1

OPERATION (Refer to Block Diagram)

Alternatively, the TRACK/SS pin can be used to force the

start-up of VOUT to track the voltage of another supply.

Typically this requires connecting the TRACK/SS pin to

an external divider from the other supply to ground (see

the Applications Information section). It is only possible

to track another supply that is slower than the internal

soft-start ramp. The TRACK/SS pin also has an internal

open-drain NMOS pull-down transistor that turns on to

reset the TRACK/SS voltage when the channel is shut

down (RUN = 0V or VCC < UVLO threshold) or during an

OC fault condition.

No external PLL filter is required to synchronize the

LTC7851/LTC7851-1 to an external clock. Applying an

external clock signal to the CLKIN pin will automatically

enable the PLL with internal filter.

In multiphase operation, one master error amplifier is used

to control all of the PWM comparators. The FB pins for

the unused error amplifiers are connected to VCC in order

to three-state these amplifier outputs and the COMP pins

are connected together. When the FB pin is tied to VCC,

the internal 2.5µA current source on the TRACK/SS pin

is disabled for that channel. The TRACK/SS pins should

also be connected together so that the slave phases can

detect when soft-start is complete and to synchronize the

nonsynchronous mode of operation.

The LTC7851/LTC7851-1 feature a CLKOUT pin, which

allows multiple LTC7851/LTC7851-1 ICs to be daisy

chained together in multiphase applications. The clock

output signal on the CLKOUT pin can be used to synchronize

additional ICs in a multiphase power supply solution feeding

a single high current output, or even several outputs from

the same input supply.

Frequency Selection and the Phase-Locked Loop (PLL)

The selection of the switching frequency is a trade-off

between efficiency, transient response and component

size. High frequency operation reduces the size of the

inductor and output capacitor as well as increasing the

maximum practical control loop bandwidth. However,

efficiency is generally lower due to increased transition

and switching losses.

The LTC7851/LTC7851-1’s switching frequency can be

set in three ways: using an external resistor to linearly

program the frequency, synchronizing to an external clock,

or simply selecting one of two fixed frequencies (600kHz

and 1MHz). Table 1 highlights these modes.

Table 1. Frequency Selection

CLKIN PIN

FREQ PIN

FREQUENCY

Clocked

RFREQ to GND

250kHz to 2.25MHz

High or Float

RFREQ to GND

250kHz to 2.25MHz

Low

Low

600kHz

Low

High

1MHz

Constant-frequency operation brings with it a number of

benefits: inductor and capacitor values can be chosen

for a precise operating frequency and the feedback loop

can be similarly tightly specified. Noise generated by the

circuit will always be at known frequencies.

Using the CLKOUT Pin in Multiphase Applications

The phase relationship among each channel, as well as the

phase relationship between channel 1 and CLKOUT, are

summarized in Table 2. The phases are calculated relative to zero degrees, defined as the rising edge of PWM1.

Refer to Application Information for more details on how

to create multiphase applications.

Table 2. Phase Relationship

CH-1

0°

CH-2

180°

CH-3

90°

CH-4

270°

CLKOUT

45°

Using the LTC7851/LTC7851-1 Error Amplifiers in

Multiphase Applications

Due to the low output impedance of the error amplifiers,

multiphase applications using the LTC7851/LTC7851-1

use one error amplifier as the master with all of the slaves’

error amplifiers disabled. The channel 1 error amplifier

(phase = 0°) may be used as the master with phases 2

through n (up to 12) serving as slaves. To disable the

slave error amplifiers, connect the FB pins of the slaves

Rev A

For more information www.analog.com

15

�LTC7851/LTC7851-1

OPERATION (Refer to Block Diagram)

to VCC. This three-states the output stages of the amplifiers. All COMP pins should then be connected together

to create PWM outputs for all phases. As noted in the

section on soft-start, all TRACK/SS pins should also be

shorted together. Refer to the Multiphase Operation section in Applications Information for schematics of various

multiphase configurations.

Theory and Benefits of Multiphase Operation

Multiphase operation provides several benefits over traditional single phase power supplies:

Greater output current capability

n

Improved transient response

n

Reduction in component size

n

Increased real world operating efficiency

n

Because multiphase operation parallels power stages,

the amount of output current available is n times what it

would be with a single comparable output stage, where

n is equal to the number of phases.

The main advantages of PolyPhase operation are ripple

current cancellation in the input and output capacitors, a

faster load step response due to a smaller clock delay and

reduced thermal stress on the inductors and MOSFETs

due to current sharing between phases. These advantages

allow for the use of a smaller size or a smaller number

of components.

Power Good Indicator Pins (PGOOD)

Each PGOOD pin is connected to the open drain of an

internal pull-down device which pulls the PGOOD pin

low when the corresponding VSNSOUT pin voltage is

outside the PGOOD regulation window (±7.5% entering

regulation, ±10% leaving regulation). The PGOOD pins

16

are also pulled low when the corresponding RUN pin is

low, or during UVLO.

When the VSNSOUT pin voltage is within the ±10% regulation window, the internal PGOOD MOSFET is turned off

and the pin is normally pulled up by an external resistor.

When the VSNSOUT pin is exiting a fault condition (such

as during normal output voltage start-up, prior to regulation), the PGOOD pin will remain low for an additional

30μs. This allows the output voltage to reach steady-state

regulation and prevents the enabling of a heavy load from

retriggering a UVLO condition.

In multiphase application, only the master phase differential

and error amplifiers are used to control all phases. The

slave phase differential amplifiers are three-stated. The

slave phase VSNSOUT pins are connected to the master

phase VSNSOUT pin to obtain output voltage information. Only the PGOOD output for the master control error

amplifier should be connected to the fault monitor.

PWM Pins

The PWM pins are three-state compatible outputs, designed to drive MOSFET drivers, DrMOSs, power blocks,

etc., which do not represent a heavy capacitive load. An

external resistor divider may be used to set the voltage

to mid-rail while in the high impedance state.

Line Feedforward Gain

In a typical LTC7851/LTC7851-1 circuit, the feedback loop

consists of the line feedforward circuit, the modulator, the

external inductor, the output capacitor and the feedback

amplifier with its compensation network. All these components affect loop behavior and need to be accounted

for in the loop compensation. The modulator consists of

the PWM generator, the external output MOSFET drivers

and the external MOSFETs themselves. The modulator

gain varies linearly with the input voltage. The line feedforward circuit compensates for this change in gain, and

provides a constant gain from the error amplifier output

to the inductor input regardless of input voltage. From a

feedback loop point of view, the combination of the line

feedforward circuit and the modulator looks like a linear

voltage transfer function from COMP to the inductor input

and has a gain roughly equal to 12V/V.

Rev A

For more information www.analog.com

�LTC7851/LTC7851-1

APPLICATIONS INFORMATION

Output Voltage Programming and Differential Output

Sensing

More precisely, the VOUT value programmed in the previous

equation is with respect to the output’s ground reference,

and thus, is a differential quantity. The minimum differential

output voltage is limited to the internal reference, 0.6V,

and the maximum differential output voltage is VCC – 0.5V.

The LTC7851/LTC7851-1 integrate differential output sensing with output voltage programming, allowing for a simple

and seamless design. As shown in Figure 3, the output

voltage is programmed by an external resistor divider

from the regulated output point to its ground reference.

The resistive divider is tapped by the VSNSP pin, and the

ground reference is sensed by VSNSN. An optional feedforward capacitor, CFF, can be used to improve the transient

performance. The resulting output voltage is given according to the following equation:

The VSNSP pin is high impedance with no input bias

current. The VSNSN pin has about 7.5μA of current flowing out of the pin. Differential output sensing allows for

more accurate output regulation in high power distributed

systems having large line losses. Figure 4 illustrates the

potential variations in the power and ground lines due

to parasitic elements. These variations are exacerbated

in multi-application systems with shared ground planes.

Without differential output sensing, these variations directly

reflect as an error in the regulated output voltage.

⎛ R ⎞

VOUT = 0.6 V • ⎜ 1 + FB2 ⎟

⎝

RFB1 ⎠

The LTC7851/LTC7851-1’s differential output sensing

scheme is distinct from conventional schemes. In conventional schemes, the regulated output and its ground

reference are directly sensed with a difference amplifier

whose output is then divided down with an external resistive divider and fed into the error amplifier input. This

conventional scheme is limited by the common mode

input range of the difference amplifier and typically limits

differential sensing to the lower range of output voltages.

VOUT

LTC7851/

LTC7851-1

CFF

(OPT)

RFB2

COUT

VSNSP

RFB1

VSNSN

7851 F03

The LTC7851/LTC7851-1 allow for seamless differential

output sensing by sensing the resistively divided feedback

voltage differentially. This allows for differential sensing

in the full output range from 0.6V to VCC – 0.5V. The dif-

Figure 3. Setting Output Voltage

CIN

MT

LTC7851/

LTC7851-1

VSNSP

RFB2

VSNSN

RFB1

+

–

VIN

POWER TRACE

PARASITICS

L

±VDROP(PWR)

MB

COUT1

ILOAD

COUT2 I

LOAD

GROUND TRACE

PARASITICS

±VDROP(GND)

OTHER CURRENTS FLOWING IN

SHARED GROUNDPLANE

7851 F04

Figure 4. Differential Output Sensing Used to Correct Line Loss Variations

in a High Power Distributed System with a Shared Ground Plane

Rev A

For more information www.analog.com

17

�LTC7851/LTC7851-1

APPLICATIONS INFORMATION

ference amplifier of the LTC7851/LTC7851-1 has a gain

bandwidth of 40MHz, high enough not to affect main

loop compensation and transient behavior. To avoid noise

coupling into VSNSP, the resistor divider should be placed

near the VSNSP and VSNSN pins and physically close to

the LTC7851/LTC7851-1. The remote output and ground

traces should be routed parallel to each other as a differential pair to the remote output. These traces should be

terminated as close as physically possible to the remote

output point that is to be accurately regulated through

remote differential sensing. In addition, avoid routing

these sensitive traces near any high speed switching

nodes in the circuit. Ideally, they should be shielded by a

low impedance ground plane to maintain signal integrity.

Programming the Operating Frequency

The LTC7851/LTC7851-1 can be hard wired to one of two

fixed frequencies, linearly programmed to any frequency

between 250kHz and 2.25MHz or synchronized to an

external clock.

Table 1 in the Operation section shows how to connect the

CLKIN and FREQ pins to choose the mode of frequency

programming. The frequency of operation is given by the

following equation:

Frequency = (RFREQ – 19.8kΩ) • 33.5Hz/Ω,

when Frequency is