LMH1983 Evaluation Kit Users Guide

LMH1983 Evaluation Kit Users Guide

Version 1.0

2/4/10

Page 1 of 25

�LMH1983 Evaluation Kit Users Guide

INTRODUCTION

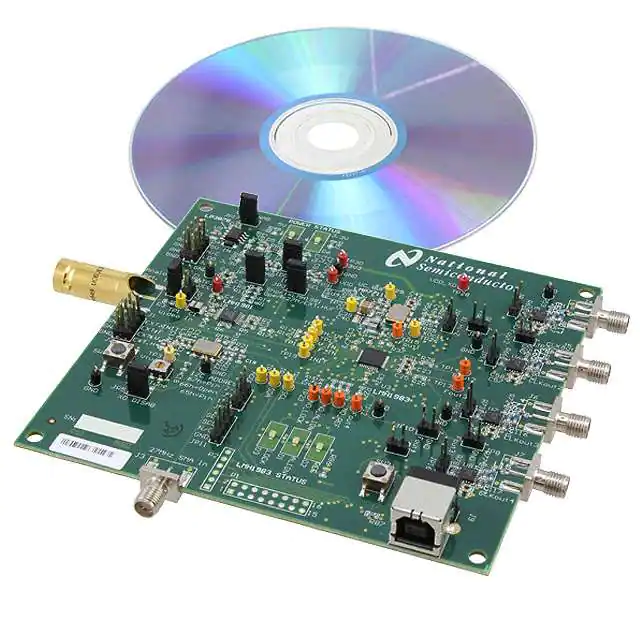

The LMH1983 Evaluation Kit (EVK) allows for the evaluation of the LMH1983

3G/HD/SD Video Clock Generator with Audio Clock. The LMH1983 device is

configured and controlled using National Semiconductor’s Analog Launch Pad (ALP)

software graphical user interface (GUI).

The GUI with the LMH1983 profile runs on Windows PC and can be used to program the

device’s control registers through the I2C interface. The Serial Peripheral Adapter (SPA)

board included in the kit provides I2C read/write control via the USB port of the PC with

the GUI. For more information about the GUI software and device register descriptions

and programming, please refer to the GUI software manual and LMH1983 datasheet.

Overview of LMH1983

The LMH1983 clock generator generates four video specific clocks. The device has four

PLLs in it.

PLL1 uses an external 27 MHz VCXO, and always generates a 27MHz reference

clock. This clock may be locked to an input reference which can be any of a

number of different types of reference – from video specific references to single

frequency reference signals.

PLL2 is dedicated to generating a 148.5 MHz clock (27 MHz * 5.5) , and is

locked to PLL1.

PLL3 is dedicated to generating a clock at 148.35 MHz (27 MHz * 5500/1001)

PLL4, by default is locked to PLL1, and generates a 24.576MHz clock which can

be used as an audio clock. PLL4 has a lot of versatility built in to it and can be

used for a broad variety of applications.

Page 2 of 25

�LMH1983 Evaluation Kit Users Guide

LMH1983 EVALUATION BOARD OVERVIEW

The following block diagram shows an overview of the LMH1983 evaluation board and

general location of the main features, which will be discussed in the following sections of

this manual.

Power

Header

Power LEDs

J8

LP

3878

CLKout1

SMA

LPF

Analog

Ref. In BNC

J1

LMH

1981

J2

Syncs

Quad

2:1

MUX

VCXO

X1

J4

HVF

inputs

CLKout2

SMA

J5

LMH1983

CLKout3

SMA

J6

EXT.HVF

VCXO

X2

CLK In

SMA

CLK

(VCXO

or SMA)

CLKout4

SMAs

USB

Port

J7

J9

Status LEDs

J3

Applying power to the board:

The default configuration to apply power is to apply +5V across the top two pins on J8.

With a jumper on JP17, and on board LDO is used to generate the 3.3V rail that powers

the circuits on the evaluation board.

Alternately, JP17 may be removed, and a 3.3V rail may be applied directly to the bottom

two pins of J8.

Page 3 of 25

�LMH1983 Evaluation Kit Users Guide

Installing the software:

The evaluation kit contains a CD which has the control software on it. Running the

program on the CD will install the software on your computer.

Apply power to the Evaluation Board, and then attach a USB cable between the computer

and the board. Windows will recognize the board and pop up the

When this window comes up, select ‘No, not this time’ and ‘Next>’

Page 4 of 25

�LMH1983 Evaluation Kit Users Guide

Select “Install from a list or specific location”

Page 5 of 25

�LMH1983 Evaluation Kit Users Guide

Page 6 of 25

�LMH1983 Evaluation Kit Users Guide

For the location, enter “C:\Program Files\National Semiconductor Corp\Analog

Launchpad Vxxx\DRIVERS” This directory was installed on your computer during the

ALP software installation.

The computer will warn you that the software has not passed Windows Logo Testing. Go

ahead and Continue Anyway.

The driver for the LMH1983 evaluation board will now be installed, and you can start the

ALP software.

When you start the Analog LaunchPAD software, it should recognize the evaluation

board and the screen will look like the figure below.

If the board is not connected properly, or not powered up, the ALP software will start up

in a demo mode which will look like the normal mode, but will not control the board.

Once the startup screen appears, click on the LMH1983 icon on the left side of the

window, and this will bring up the GUI:

Page 7 of 25

�LMH1983 Evaluation Kit Users Guide

The status indications on the GUI are only updated when the Read Controls/Status button

is clicked. To have continuous updates, click the checkbox ‘Auto Refresh Status’, I also

like to check the ‘Perform ReadAll after write’ box – this will update all of the status

controls whenever something is written. In some cases, writing to one register will result

in multiple things changing, and checking this button will make sure that everything is

kept updated.

There are several panels in the GUI - the first is the main control panel and allows for

basic control over the board. Also very useful is the Registers tab, which will allow for

detailed manipulation of the various registers in the LMH1983.

Page 8 of 25

�LMH1983 Evaluation Kit Users Guide

I2C SLAVE ADDRESS

The I2C address select jumper JP9 (3-way) can be configured as follows to select one of

the three I2C slave addresses offered by the LMH1983. The default for the board, and

for the ALP software is address ‘66h which corresponds to no jumper installed.

Table 1: LMH1983 I2C Slave Address Selection

7-bit I C Slave Address

JP1 Jumper Setting

LMH1983 Address Input State

65’h (hex)

Short Pins 1-2

Externally tied low

66’h

Open Pins

Internally biased to mid-supply

67’h

Short Pins 2-3

Externally tied high

2

Observing the Outputs

The LMH1983 generates four clock signals (CLKout1, CLKout2, CLKout3, CLKout4)

and four timing signals (TOF1, TOF2, TOF3, TOF4). The LMH1983 outputs are

differential outputs, and can be observed directly at JP13, JP14, JP15 and JP16. There

are 100Ω termination resistors situated near the connectors (R60,R66, R73 and R78). If

the differential signals are to be observed with a high impedance differential scope probe,

it can be attached directly to the pins. If it is desired that the differential outputs drive a

load, the load resistor should be moved to be adjacent to the final load. In addition to the

differential outputs, there are 50Ohm single ended outputs as well. These are provided

by using LMH0302 SDI cable drivers. On the initial version of the evaluation board

these outputs exhibit some undershoot and ringing at 4GHz which degrades the jitter

performance of these outputs.

Configuring the board for operation with an analog video

reference signal

The LMH1983 Evaluation board includes an LMH1981 sync separator which is able to

extract the timing signals from a broad range of analog sync signals. To use this feature,

install a jumper on JP4 (MUX ENABLE), and one on JP3 (Input Select). Supply the

reference signal to J1 (analog Ref In), and you can monitor the extracted H, V and F

signals at the yellow test points just to the left of the LMH1983.

The GUI will display what format is being detected under the PLL1

The LMH1983 can automatically detect and synchronize to the following reference input

formats received at its input pins:

HVF Sync timing from SMPTE standard video formats

o 525i/29.97/30

o 525p/59.94/60

Page 9 of 25

�LMH1983 Evaluation Kit Users Guide

o 625i/25

o 625p/50

o 720p/23.98/24/25/29.97/30/50/59.94/60

o 1080i/25/29.97/30

o 1080p/23.98/24/25/29.97/30/50/59.94/60

o 1080pSf/23.98/24/25/29.97/30

Audio Word Clock

o 32 kHz, 48 kHz, 96 kHz, 44.1 kHz

System Clock

o 27 MHz

o 10 MHz

Configuring the board for operation with a digital video

reference signal

An external digital reference signal, consisting of H,V and F may be applied to J2, a

jumper should installed on JP5, and the jumper on JP3 should be removed.

The GUI will display what format is being detected under the PLL1

For a comprehensive list of formats that can be detected, please refer to the LMH1983

datasheet. To determine format, the device measures the period of the Hsync input by

counting 27MHz clock pulses over several Hsync periods. There are some standards

where Hsync may be the same, in which case V and F are examined to determine if the

reference is an interlaced or progressive format before format detection is complete.

Configuring the board for operation in free-run mode, using

the on board reference oscillator

To operate the board in ‘stand-alone mode’, remove the jumper for JP3, make sure that

the jumper is removed from JP5, and in this mode, the frequency can be trimmed via R20

– the trim pot near the lower left corner of the board.

Configuring the board for operation, locked to an external

clock oscillator.

To operate the board locked to an external clock, supply the reference signal through the

SMA connector ‘J3’, remove the jumper form JP3 and install a jumper on JP5.

The automatic format detect algorithm in the LMH1983 will recognize reference clocks

of 27MHz or 10MHz. Other reference rates can be manually programmed.

Page 10 of 25

�LMH1983 Evaluation Kit Users Guide

Page 11 of 25

�LMH1983 Evaluation Kit Users Guide

PLL1 LOOP FILTER AND VCXO

The LMH1983’s primary phase lock loop, PLL1, provides the following key functions:

Synchronizes the 27 MHz VCXO clock to the reference input

Attenuates (cleans) input jitter

Provides a stable, low-jitter 27 MHz clock for PLLs 2, 3, 4

The external loop filter and 27 MHz VCXO are essential to the performance of PLL1,

which dominates the overall loop response of the LMH1983. The loop response of PLL1

is influenced by the external loop components and can be characterized by its loop

bandwidth and damping factor.

PLL1 is designed for a nominal loop bandwidth of about 3 Hz (min) and damping factor

of 0.70 (min). These were calculated using the approximations below, which assume

nominal ICP1 = 250uA and DIV_N1 = 1716 for the NTSC input format:

Loop Bandwidth (BW) = R47*ICP1*KVCO / DIV_N1

Damping Factor (DF) = 0.5*R47*sqrt[ (C33 || C39)*ICP1*KVCO / DIV_N1 ]

Loop Filter

The loop filter components include R47, C39 || C40, and C33. It’s recommended to

avoid use of ceramic capacitors in the loop filter since they exhibit piezoelectric

properties that can cause electrical noise when the board/component is subjected to

vibration or shock. This “shock noise” in the loop filter circuit can result in lowfrequency phase modulation on the VCXO output clock and thus on the downstream PLL

output clocks. Tantalum and film capacitors are used for the loop filter since they do not

exhibit piezo effects.

Page 12 of 25

�LMH1983 Evaluation Kit Users Guide

Figure 1: Loop Filter and LMP7711 Buffer Schematic

Op Amp Buffer

The LMP7711 Precision, Low-Noise Op Amp (U4) is used as a buffer to isolate the

relatively low input impedance of the VCXO, which would otherwise be the dominant

source of leakage current for loop filter circuit. The op amp offers very high input

impedance to minimize this leakage current and high slew rate to ensure proper loop

operation. The VCXO input control voltage input can be measured at TP29 (VC_BUF).

Note that when the LMH1983 is operating in free run mode, the VC_LPF output set by

the user-defined free run voltage control register may be limited by the output voltage

range of the LMP7711, as it is not a rail-to-rail op amp.

Page 13 of 25

�LMH1983 Evaluation Kit Users Guide

VCXO

The 27 MHz VCXO (X2) is specified for ±50 ppm APR (min) and ±50 ppm frequency

stability. The calculated VCXO gain is 1000 Hz/V (min). The VCXO gain parameter

(KVCO) affects the PLL1 loop response, so it must be considered when designing the

nominal loop bandwidth and damping factor.

The VCXO’s single-ended output clock can be measured at TP26 (XOclk+). The VCXO

clock is received at the XOin+ input of the LMH1983. XOin+ (pin 34) and XOin- (pin

33) are differential inputs for the internal op amp that drives the clock signal to the PLL

blocks. Because XOin is a differential input, the XOin- pin is biased to about 1.25V

using a voltage divider formed by R52 and R56. This input configuration presents a

pseudo-differential signal to the XOin pins.

Alternatively, the single-ended VCXO may be replaced with a different 27 MHz VCXO

with differential clock outputs (e.g. LVDS); in this case, R52, R56, and C48 should be

removed, R54 should be populated with 49.9R to match R55, and R37 should be

populated with a 100R differential load. Using a true differential input signal can provide

more common-mode rejection and reduce noise/crosstalk, and thus reduce sources of

deterministic jitter.

INDEPENDENT AUDIO CLOCK GENERATION

By default, the audio clock generated from PLL4 is phase-locked to the 27 MHz VCXO

clock reference from PLL1, and in turn, is synchronized to the reference input.

It is possible to have the audio clock independently generated from an external 27 MHz

clock source by changing the PLL4 input mux mode via register programming. Once the

PLL4 input mode is properly programmed, pin 17 (normally Fout4) is switched to an

input pin (OSCin) and can be driven with an external 27 MHz clock.

There are two options for an independent 27 MHz clock source. The first option is to use

an on-board 27 MHz VCXO in the footprint X2. The second option is to receive an

external 27 MHz via the SMA clock input, J3. Either one of the options can be used as

long as it’s not being used to drive the Hin reference of the LMH1983. To make use of

this option, populate R21 and R28, then to use the on board oscillator, enable it by

removing the jumper on JP5, and to use the external SMA, disable the oscillator with a

jumper on JP5 and provide the reference on J3.

Page 14 of 25

�LMH1983 Evaluation Kit Users Guide

Appendix A

Schematics

Page 15 of 25

�1

2

3

4

5

6

A

A

VDD_CLK1

VDD_CLK2

VDD_CLK3

VDD_PLL34

Layout Note: Unless otherwise noted, label all

ICs, Test Points, Jumpers and Headers per the

component comment. For jumpers and headers,

label pins according to the pin legend noted. All

labels should be present on top and bottom silk

screen (except for ICs).

VDD_CLK4

PIC20 1

VDD_PLL2

PIC210

COC20

C20

PIC20 2

COC21

C21

PIC2102

1uF

COTP12

TP12

B

PIC2 01

Layout Note: On Fout* pins and pins 11, 12, 13,

place direct components as close to LMH1983 as

possible.

0.1uF

VDD_PLL1

Fout4

COTP13

TP13

Fout3

COTP14

TP14

Fout2

COTP15

TP15

Fout1

PITP1201

PITP1301

PITP1401

PITP1501

B

PIC2301

COC22

C22

PIC2 02

COC23

C23

PIC2302

1uF

0.1uF

VDD

PIC2401

H_IN

V_IN

F_IN

PITP1601

PITP1701

PITP1801

INIT

R32

OPEN

PIR3201

PITP1901

R33

OPEN

PIR3 01

R34

OPEN

PIR3401

R35

OPEN

PIR3501

R36

OPEN

PIR3601

PIC2802 OPEN

LMH1983SQ

SDA

ADDR

34

PIU3034 XOin+

33

PIU3033

XOin-

OPEN

PIC2702

PIU3013

VC_LPF

PIU3040

NLCLKout40P

CLKout4_P

NLCLKout40N

CLKout4_N

PIU3015

PIU3014

CLKout4_P

CLKout4_N

COC30

C30

OPEN

PIC3401

PIR4602

PIC3402

COC34

C34

OPEN

PIC3501

PIC3502

XOclk+

COC35

C35

Layout Note:

TP Legend is

"XO_CLK"

OPEN

PITP2601

Layout Note: Place JP3

near edge of PCB.

COC33

C33

PIC3302

Layout Note: JP Legend is

"Disable XO"

PIR4701 PIC4002

17.4k

C41

COC41

PIR5201

1uF

R52

COR52

3.0k

PIC4201

PIC4202

C42

COC42

0.1uF

PIC4301

PIC4302

NLXOin0N

XOin_N

PIR5402

PIR5401

0.01uF

5

R54 OPEN

COR54

XOin_P

PIR5502

COR55

R55

PIR5602

PIC4802

PIR5601

PIC4801

R56

COR56

LMH1983 Evaluation Board

Rev. 1

C43

COC43

PIR5202

PIX206

1.82k

COC48

C48

0.1uF

PIX205

COTP29

TP29

VC_BUF

PIC3702

COC37

C37

OPEN

PIC3801

PIC3802

COJP8

JP8

2

PIJP1002

COTP24

COTP25

TP24

TP25

NO_ALIGN NO_REF

Layout Note: Pin 17 is a programmable I/O pin.

When the pin is an output, the resistor should be

populated for net "Fout4" (default). When the pin

is an input, the other resistor should be populated

for net "OSCin". Minimize trace stubs on this

pin.

PITP2401

PITP2501

C

COR40

R40

NLNOLOCK

NOLOCK

PIR4001

PIR4002

NOLOCK

PIR4302

PIR4502

NLNOALIGN

NOALIGN

NLNOREF

NOREF

NOALIGN

NOREF

33

COC38

C38

OPEN

VDD_XO

VDD_XO

PIR4801

COR48

R48

10.0k

PIR4802

PIR4902

PIR50 1

PIU405 PIU403 PIU40

COU4

U4

LMP7711MK

PIU401

COR50

R50

OPEN

PIR50 2

6

PIU406

PIC4602

PIC4601

OUTA

VC

4

2

PIJP802

1

PIJP801

COC29

C29

OPEN

COR51 PIR5102

R51

0

COC46

C46

0.1uF

PIR5101

PITP2901

R53

COR53

1

PIX201

PIR5501PIX204 OUT

PIR5501PIX204

49.9

PIC3701

PITP2701

PIR4901

PIX20

COC36

C36

OPEN

PIC4001

OPEN

PIJ120 PIJ120

2

PIC4101

PIC4102

"Fout1" (inline w/ JP11.2)

"Fout2" (inline w/ JP12.2)

"Fout3" (inline w/ JP13.2)

"Fout4" (inline w/ JP14.2)

"GND" (inline w/ pin 1 of JP11, JP12, JP13, JP14)

COTP27

TP27

VC

PIC3901

PIU402

1uF

1

PIJP701

COR45

R45

2

6

COC45

C45

2

PIJP702

Layout Note: Pin Legend is

33

PIC3601

COR49

R49

OPEN

EN

PIC4502

10uF

Fout2

OPEN

PIR4501

PIC3301

PIL402

VCC

PIC4501

COC44

C44

COJP6

JP6

COC27

C27

PIR4 01

47uF

C40

COC40

COR47

R47

PIR4702

GND

PIC4 02

2

PIJP602

1

PIJP601

COR43

R43

COC39

C39

PIR5302

PIC4701

PIC4702

C47

COC47

OPEN

X2

COX2

PIX203

3

PIC4 01

250mA

220 ohm

Fout1

PIR4301

PIC3602

PIC3902

VDD_XO

NLOSCin

OPEN OSCin

PIR2801

COC26

C26

OPEN

PIR4 02COR44

1uF

PITP2801

NLFout4

Fout4

COR28

R28

PIR2802

1

PIJP1001

R44

0

L4

COL4

33

Fout4

PIU3018 PIU3021 PIU30 9 PIU3041

COJP12

JP12

PIL401

PIR2701

33

VDD_XO

3V3

PIC2902

PITP2301

COTP28

TP28

Layout Note: TP Legend is

"VDD_XO"

PIC30 1

PIC30 2

COTP23

TP23

1

PIR4601COR46

NLFout3

Fout3

COR27

R27

PIR2702

40

4

COTP26

TP26

NLFout2

Fout2

33

COJP10

JP10

13

12

11

PIU3011

3

NLXOin0P

PIR4202

33

33

PIR2601

PIU3012

2

1

PIR4201

PIR2501

COR26

R26

PIR2602

COJP7

JP7

18

21

39

PIR4102

4.75k

COR25

R25

PIR2502

Fout3

NO_LOCK

XOin_N

XOin_P

COR42

R42

PIJP1104

Pin Legend is:

"GND" (pin 1)

"N/C" (pin 2)

"SCL" (pin 3)

"SDA" (pin 4)

NO_REF

NO_ALIGN

NO_LOCK

PIR3702

OPEN

PIJP1103

R46

OPEN

17

15

14

PIU3017

NLFout1

Fout1

CLKout3_N

CLKout3_P

PIC2901

5

PIR3701

PIJP1102

COJP11

JP11

PIC2701

PIU3022

COR37

R37

PITP2 01

PIR3802

33

COR41

R41

PIR4101

PIJP1101

SCL

COC31

C31

100 OHM DIFF. IMPEDANCE

1

2

3

4

0.1uF

PIR3801

4.75k

COC32

C32

PIC3202

PITP210

COR38

R38

COR39

R39PIR3901

PIC3102

PIC3101

COTP22

TP22

SDA

3V3

PIC3201

PIU3023

PIC2602

CLKout2_N

CLKout2_P

NLCLKout30N

CLKout3_N

NLCLKout30P

CLKout3_P

24

23

22

PIU3024

Fout4/OSCin

CLKout4+

CLKout4-

GND

GND

GND

DAP

COTP21

TP21

PIR3902

NLCLKout20N

CLKout2_N

NLCLKout20P

CLKout2_P

33

PIR2401

PIC2601

CLKout1_P

CLKout1_N

SCL

PITP20 1

C

NLCLKout10P

CLKout1_P

NLCLKout10N

CLKout1_N

30

Fout2

29

CLKout2- PIU3029

28

CLKout2+ PIU3028

VV+

3

PIJP903

2

PIJP902

1

PIJP901

37

Fout1 PIU3037

36

CLKout1+ PIU3036

35

CLKout1- PIU3035

CLKout3CLKout3+

Fout3

U3

COU3

PIU308

0.1uF

27

26

25

38

31

20

16

7

ADDR

8

SDA

9

PIU309

SCL

PIU307

COC28

C28

COC25

C25

PIC2502

1uF

PIU3030

COTP20

TP20

3V3

D

1

32

19

3

Hin

4

PIU304 Vin

5

PIU305

Fin

6

PIU306

INIT

PIU303

PIR3 02COR33 PIR3402COR34 PIR3502COR35 PIR3602COR36 PIC2801

COJP9

JP9

I2C CONN

R31

OPEN

PIR3101

HIN

VIN

FIN

INIT

Layout Note:

Pin legend is:

"65h = Pin 1-2"

"66h = Float Pin 2"

"67h = Pin 2-3"

I2C ADDR SEL

R30

OPEN

PIR30 2

PIC2402

PIU3027 PIU3026 PIU3025

Cbyp2

Cbyp4

Cbyp3

R29

OPEN

PIR2902

PIU30 8 PIU30 1 PIU302 PIU3016

VDD_CLK1

VDD_CLK2

VDD_CLK3

VDD_CLK4

PIR2901COR29 PIR30 1COR30 PIR3102COR31 PIR320 COR32

VDD_IO

VDD_IO

COTP16

TP16 COTP17

TP17 COTP18

TP18 COTP19

TP19

PIU301 PIU30 2 PIU3019

VDD_PLL1

VDD_PLL2

VDD_PLL34

2

10

PIU302 PIU301

VDD

PIC2501

COC24

C24

COR24

R24

PIR2402

357LB3I027M0000

Layout Note: XO Legend is

"27MHz VCXO"

PLL1 Loop Filter and VCXO

PIR5301

0

Note: XOin pair can be driven by a VCXO with LVCMOS clock

or LVDS clock.

D

-LVCMOS (default):

XOin+: Connect to VCXO's single-ended output.

XOin-: Bias to 1.65VDC via 1.00k divider resistors using the

VCXO's supply (VDD_XO) and local ground for optimal CMR.

OUTA (VCXO pin 5): No connect (N/C)

Title

-LVDS:

XOin+/-: Connect to VCXO's LVDS output and terminated with

100R differential.

OUTA: Complementary LVDS output pin. Remove 1k resistors

and 0.1uF cap and install series resistor.

LMH1983 Eval Board - LMH1983

Size

Date:

File:

1

2

3

4

Number

Revision

B

C

5

11/3/2009

Sheet 4 of 5

C:\Projects\..\LMH1983 Demo Board.SchDocDrawn By: Sauerwald

6

�1

2

3

4

5

6

VDD

A

CLKout1_P

COC49

C49

NLCLKout10P

CLKout1_P

PIC4901 PIC4902

COR60

R60

PIR6001

6

PIU506

COJP13

JP13

10

PIU5010

PIR6002

100

ENABLE

SD/HD

1

PIU501

SDI

2

PIU502

SDI

COC50

C50

NLCLKout10N

CLKout1_N

4

PIU504

PIC5301

COC53

C53

PIC5302 0.1uF

9

PIU509

PIR5702

PIR5802

PIR5902

COR61

R61

PIR6101

PIR6102

2

1

PIJP1401

PIC5401 PIC5402

PIR6601

0 ohm (10nF)

3V3

17

PIU5017

3

PIU503

B

CLKout2_P

6

10

PIU6010

PIR6602

ENABLE

SD/HD

PIC5701

PIC5702

PIC5801

PIC5802

C57

COC57

1uF

9

0.1uF

PIU609

PIR6402

49.9

PIC11902

PIR6701

1

PIJ50 PIJ504 PIJ503 PIJ502

PIR6702

PIC5 01

PIC5 02

750

16

PIU6016

PIR70 1

PIC6001 PIC6002

2

1

PIJP1501

15

PIU6015

14

PIU6014

13

PIU6013

8

PIU608

7

PIU607

5

PIU605

NLCLKout30P

CLKout3_P

C61

COC61

PIC6101 PIC6102

COU7

U7

6

10

PIU706

COJP15

JP15

R73

COR73

PIR7301

PIU7010

PIR7302

100

ENABLE

SD/HD

1

PIU701 SDI

2

PIU702 SDI

0 ohm (10nF)

C

COR70

R70

49.9

SDO

SDO

RREF

CLKout4_P

NLCLKout40P

CLKout4_P

C62

COC62

1uF

PIC6301

PIC6302

C63

COC63

9

PIU709

0.1uF

12

11

3V3

PIR7102

PIC5901

PIC5902

PIR7201

COR72

R72

49.9

4

PIU704

PIC11602

PIR7401

COC59 D3

COD3

C59

0.1uF

PID301

1

COR68

R68

PIR6801

NOREF

Layout Note: Place LEDs nearby

status flag pins.

LED Legend 'LOCK'

LG M670-J2M1-1-0-10-R18-Z

COR69

R69

150

PIR6901

NOLOCK

CLKout3

PIC11601

PIJ601

PIR7402

B

LG M670-J2M1-1-0-10-R18-Z

PIR6902

0.1uF

COR74

R74

PID302

COJ6

J6

COC116

C116

PIR7202

PIU7011

PIJ605 PIJ604 PIJ603 PIJ602

750

C

17

3

PIU7017

VDD

PIU703

2

1

PIJP1602

JP16

COJP16

R78

COR78

COC65

C65

PIR7801

PIC6501 PIC6502

PIR7802

100

6

PIU806 ENABLE

10

PIU8010 SD/HD

12

SDO PIU8012

11

SDO PIU8011

1

SDI

2

PIU802 SDI

RREF

PIU801

VDD

C66

COC66

1uF

PIC6701

PIC6702

C67

COC67

0.1uF

9

PIU809

DAP

VEE

VCC

LMH0302SQ

2

4

PIU804

16

NC PIU8016

15

NC PIU8015

14

NC PIU8014

13

NC PIU8013

8

NC PIU808

7

NC PIU807

5

PIU805

NC

D

PIC6 01

PIC6 02

PIR7501

PIR7601

PIR7 01

PIR7502

PIR7602

PIR7 02

COR75 COR76

R75

R76

49.9 49.9

COU8

U8

PIJP1601

0 ohm (10nF)

1

COR71

R71

49.9

PID201

150

PIC6401 PIC6402

100 OHM DIFF. IMPEDANCE

CLKout4_N

NLCLKout40N

COC55 D2

COD2

C55

0.1uF

Layout Note: Place LEDs nearby

status flag pins.

LED Legend 'REF'

LMH0302SQ

C64

COC64

0 ohm (10nF)

CLKout4_N

DAP

VEE

VCC

PID20

PIR6802

PIU7012

16

NC PIU7016

15

NC PIU7015

14

NC PIU7014

13

NC PIU7013

8

PIU708

NC

7

NC PIU707

5

NC PIU705

VDD

PIC6201

PIC6202

PIR70 2

PIR7101

NOALIGN

3

17

3

PIU8017

PIU803

COR77

R77

49.9

0.1uF

COR79

R79

PIR7901

PIR7902

COJ7

J7

COC117

C117

PIC11702

1

PIC11701

PIJ701

CLKout4

PIJ705 PIJ704 PIJ703 PIJ702

5

4

3

2

100 OHM DIFF. IMPEDANCE

CLKout3_P

PIJP1502

3V3

CLKout2

PIC11901

PIJ501

0.1uF

COR67

R67

4

PIU604

PIR6201

COJ5

J5

COC119

C119

PIR6502

17

DAP PIU6017

3

VEE PIU603

VCC

COC60

C60

0 ohm (10nF)

COR62

R62

5

4

3

2

CLKout3_N

LG M670-J2M1-1-0-10-R18-Z

COR65

R65

49.9

LMH0302SQ

VDD

NLCLKout30N

CLKout3_N

PID101

PIR6501

COR64

R64

11

PIU6011

NC

NC

NC

NC

NC

NC

NC

C58

COC58

PIR6401

PIU6012

RREF

VDD

PIR6302

12

SDO

SDO

PIC5601 PIC5602

0 ohm (10nF)

COC51 D1

COD1

C51

0.1uF

Layout Note: Place LEDs nearby

status flag pins.

LED Legend 'ALIGN'

150

COR63

R63

49.9

1

PIU601

SDI

2

PIU602

SDI

100 OHM DIFF. IMPEDANCE

COC56

C56

NLCLKout20P

CLKout2_P

PIC5101

PIC5102

PID102

PIR6202

PIU606

100

A

Layout note: Place termination resistor, two pin header and

LMH0302 inputs as close together as possible. Place LMH0302

close to the board edge and the SMA connector connected to it's

output. Label SMAs on Silkscreen with CLKout1, CLKout 2 etc..

COU6

U6

COJP14

JP14

COR66

R66

LED Indicators for LMH1983 Status Flags

750

PIR6301

NLCLKout20N

CLKout2_N

CLKout1

PIJ405 PIJ40 PIJ403 PIJ402

VDD

PIJP1402

CLKout2_N

1

PIC11801

PIJ401

0.1uF

LMH0302SQ

COC54

C54

COJ4

J4

COC118

C118

15

PIU5015

14

PIU5014

13

PIU5013

8

PIU508

7

PIU507

5

PIU505

DAP

VEE

VCC

COR59

R59

49.9

PIC11802

16

PIU5016

NC

NC

NC

NC

NC

NC

NC

0 ohm (10nF)

PIC5201

COC52

C52

PIC5202 1uF

PIR5901

COR58

R58

49.9

11

PIU5011

RREF

VDD

PIC5001 PIC5002

12

PIU5012

SDO

SDO

100 OHM DIFF. IMPEDANCE

CLKout1_N

PIR5801

5

4

3

2

0 ohm (10nF)

PIR5701

COR57

R57

49.9

COU5

U5

1

PIJP1301

5

4

3

2

2

PIJP1302

750

D

National Semiconductor and/or its licensors do not warrant the accuracy or completeness of

this specification or any information contained therein. National and/or its licensors do not

warrant that this design will meet the specifications, will be suitable for your application or fit

for any particular purpose, or will operate in an implementation. National and/or its licensors

do not warrant that the design is production worthy. You should completely validate and test

your design implementation to confirm the system functionality for your application.

4

Designed for: PRJ_Customer

Mod. Date: 11/3/2009

Project: PRJ_Title

Sheet Title: Output

Sheet: 1 of 1

Size: B

Schematic: 870PRJ_BasePN Rev: SCH_Rev

Assembly Variant: variantName: No Variant Selected

File: Output.SchDoc

PADC: PRJ_PADC http://www.national.com

Contact: TechSupport

© Copyright, National Semiconductor, 2009

5

6

�1

2

3

4

5

6

Analog Input and LMH1981 Sync Separator

COU1

U1

COR1

R1

PIR102

COTP1

TP1

COC1

C1

VIDEO IN

A

COJ1

J1

COR3

R3

PIJ101

Ref. In

PIJ1032

COJP1

JP1

PIR302

2

PIJP102

PIC102

PITP101

PIR301

0

2

PIJP202

1

PIJP101

PIC202

PIC702

PIC901

PIC902

LPF ENAB

75.0

2

PIU102

VCC

3

PIU103

PIC201

0.1uF

PIC701

COC8

C8

1

PIJP201

COR4

R4 75R TERM

PIR402

PIU101

COC2

C2

PIC101

1uF

COC7

C7

COJP2

JP2

PIR401

1

PIR101

10.0k 1%

OPEN

PIC802

COC9

C9

0.1uF

560pF

OEOUT

COR2

R2

14

PIU1014

GND

BPOUT

13

PIU1013

VCC

CSOUT

12

PIU1012

PIR202

PIR201

33

NLFSYNC0A

FSYNC_A

COTP2

TP2

VCC

4

PIU104

Video In

VCC

11

PIU1011

5

PIU105

GND

GND

10

PIU1010

VCC

PIC801

Rext

6

PIU106

VCC

VFOUT

9

PIU109

7

PIU107

HSOUT VSOUT

8

PIU108

PIC301

PIC302

COR5

R5

PIR502

3V3

VCC

COL1

L1

PITP201

PIC401

PIC402

COC3

C3

0.1uF

PIR501

A

PIL102

COC4

C4

1uF

PIL101

PIC501

PIC502

220 ohm

250mA

PIC601

PIC602

COC5

C5

1uF

COC6

C6

10uF

Layout Note: Unless otherwise noted, label all

ICs, Test Points, Jumpers and Headers per the

component comment. For jumpers and headers,

label pins according to the pin legend noted. All

labels should be present on top and bottom silk

screen (except for ICs).

NLVSYNC0A

VSYNC_A

33

LMH1981MT

Layout Note: IC Legend is

"LMH1981 Sync Separator"

COR6

R6

PIR602

NLHSYNC0A

HSYNC_A

PIR601

33

3V3

External HVF+INIT Input Header

COSW1

1 SW1

Quad SPDT Input MUX with Output Hi-Z

3

PISW101

Layout Note: JP Legend is

"Short = LMH1981"

"Open = 27M/EXT HVF"

PISW103

B

2

COJ2

J2

1

PIJ201

1

Layout Note: Pin Legend is

8

PIR802

3V3

PISW104

COJP3

JP3

FSM2JSMA

COR8

R8

8

PIJ208

PIR801

NLINIT

INIT

2

PIJ202

2

7

COR10

R10

7

PIJ207

PIR1002

3

3

PIJ203

"EXT H" (inline w/ pin 5)

6

PIR1001

COR13

R13

6

PIJ206

PIR1302

NLFSYNC0B

FSYNC_B

PIR1301

Note: If U4 is not populated,

shorts can be installed to

directly connect the HVF

signals to the LMH1983 inputs.

NLVSYNC0B

VSYNC_B

33

"GND" (inline w/ pins 1-4)

4

4

PIJ204

5

COR15

R15

5

PIJ205

PIR1502

PIR1501

COR16

R16

OPEN

GND

VIN

COR18

R18

5K

PIR20 3

PIC1401

PIC1402

6

VCC

2

EN

VC

PIX103

OUT

C19

COC19

1

PIJ301

2

3

4

5

PIJ302 PIJ30 PIJ304 PIJ305

PIC1902 PIC1901

50-OHM CONTROLLED IMPEDANCE

0.1uF

PIL302

C15

COC15

1uF

NLHSYNC0B

HSYNC_B

PIR1901

33

R21

COR21

3

27MHz SMA In

NO4

VSYNC_APIU205

5

NLVIN

VIN

7

PIU207

NC2

COM4

13

PIU2013

NC3

PIU2010

COM3

PIU209

PIL201

PIC1201

PIC1202

220 ohm

250mA

COC13

C13

10uF

Note:

Short = Enable

Open = Hi-Z

10

FSYNC_B

9

NLFIN

FIN

PIR1702

COR17

R17

OPEN

PIR1701

FIN

C

PIR2102

NLOSCin

OSCin

PIR2101

OPEN

3V3

PIR2 01

PIL301

220 ohm

250mA

PIC1601

PIC1602

C16

COC16

1uF

PIC1701

PIC1702

C17

COC17

10uF

Layout Note: Distribute GND test

points around the PCB.

TP4

COTP4

TP5

COTP5

GND

TP6

COTP6

GND

PITP501

TP7

COTP7

GND

PITP601

TP8

COTP8

GND

PITP701

TP9

COTP9

GND

PITP801

TP10

COTP10

GND

PITP901

TP11

COTP11

GND

PITP10 1

GND

PITP1 01

Note: 27 MHz Clock Source can come from

either the on-board VCXO or the SMA Input.

If the SMA Input is used, the VCXO output

should be disabled. The SMA input signal

can be AC or DC coupled, and terminated

and.or biased as needed using the available

resistor options.

Layout Note: Minimize

stub length of the traces

on 27M net.

OPEN

NL27M

PIR2 02

27M

D

Title

PIR2301

LMH1983 Eval Board - LMH1981

COR23

R23

OPEN

Size

PIR2302

Number

Revision

B

B

Date:

File:

1

PIC1301

PIC1302

COC12

C12

1uF

MUX ENAB

PIJP401

PIR1401

OPEN

11 FSYNC_A

PIU2011

NO3

GND

PIR1101

COR14

R14

COM2

PIL202

COC11

C11

1uF

OPEN

12

PIU2012

PIR1402

NO2

PIC1 01

PIC1 02

COJP4

JP4

2

1

PIJP402

COR11

R11

14

PITP401

COR19

R19

4

R22

COR22

COJ3

J3

PIC1501

PIC1502

C14

COC14

0.1uF

PIX104 PIR1902

ASVV-27.000MHZ-N152-T

Layout Note:

XO Legend is

"27 MHz VCXO Source"

D

COM1

NLHINPIU204

HIN

4

15

PIU2014 PIR1102

0.1uF

COL3

L3

PIX102 PIX106

GND

COR20

R20

NC4

PIR902

COC10

C10

3V3

PIR1801

OPEN

PITP301

1

PIX101

PIC1802

COC18

C18

PIC1801 C0G/NP0: 0.1uF

EN

NO1

PIC10 1

PIC10 2

Layout Note: Place U4 on

bottom side of PCB, and

do not label IC.

1

2

PIJP502

PIR1802

PIR2002

PIU2015

NC1

VSYNC_BPIU206

6

PIR1601

V+

COR9

R9

10.0k

TS3A5018PW

PIJP501

COX1

X1

PIR1201

IN

16

PIU2016

HSYNC_BPIU203

3

8

COJP5

JP5

Layout Note:

Pot Legend is

"VCXO TUNE"

PIR901

HSYNC_APIU202

2

PIU208

27 MHz Clock Source from VCXO or SMA Input

TP3

COTP3

HIN

PIR1602

Layout Note: Minimize stub

length of HSYNC_B

EXT HVF IN

PIR1202

COR12

R12

OPEN

HSYNC_B

OPEN

PIR20 1

PIR701

10.0k

1

PIU201

33

"EXT V" (inline w/ pin 6)

Vtune

PIR702

PIJP301

COU2

U2

"EXT F " (inline w/ pin 7)

XO DISAB

COL2

L2

COR7

R7

2

1

PIJP302

INPUT SEL

INIT

33

"EXT INIT" (inline w/ pin 8)

C

B

4

PISW102

2

3

4

5

11/3/2009

C:\Projects\..\LMH1981.SchDoc

Sheet 4 of 5

Drawn By: Sauerwald

6

�1

2

3

4

Power Supply Input and Low-Noise 3.3V LDO Regulator

A

COD4

D4

Layout Note: Unless otherwise noted, label all

ICs, Test Points, Jumpers and Headers per the

component comment. For jumpers and headers,

label pins according to the pin legend noted. All

labels should be present on top and bottom silk

screen (except for ICs).

COJ8

J8

PID402

5V

1

8

PIR8101

COR81

R81

PIC6802

PIR8102

8

PIJ808

4

PIU904

PIC6801

COC68

C68

10uF

16V

PIR8401

PID502

2

7

7

PIJ807

LDO_3V3

3

PIJ803

3

6

6

PIJ806

4

PIJ804

4

5

PIC7601

PIC7602

COC92

C92

PIC8201

COC81

C81

PIC8102

COC82

C82

PIC8202

1uF

0.01uF

PIC80 1

COC80

C80

1uF PIC80 2

1uF

250mA

220 ohm

PIC105 2

1uF

PIC10602

PIC10701

0.1uF

COTP31

TP31

VDD

PIL802

VDD

PIC9301

PIC9302

PIR8201

COC72

C72

1uF

PIC7202

COR82

R82

150

PIR8202

PID602

COD6

D6

PIR8502

PID601

LG M670-J2M1-1-0-10-R18-Z

Layout Note: LED

Legend is "3.3V"

COC93

C93

1uF

PIC9401

PIC9402

COC94

C94

10uF

PIC9501

PIC9502

PITP3101

COC95

C95

10uF

VDD

VDD_PLL1

COL7

L7

PIL602

PIL701

PIC7 01

PIC7 02

PIC8301

COC77

C77

1uF

COC83

C83

PIC8302

0.01uF

COC75

C75

1uF

PIC9601

PIC9602

COC96

C96

10uF

PIC9701

PIC9702

COC97

C97

10uF

PIC9801

PIC9802

COC84

C84

1uF

COC98

C98

10uF

PIC8401

PIC8402

PIL702

PIC7501

PIC7502

PIC7801

PIC7802

250mA

220 ohm

COC78

C78

1uF

VDD

PIC7901

PIC7902

1uF

VDD_PLL2

COL9

L9

PIL801

250mA

220 ohm

PIL902

PIC8501

PIC8502

COC85

C85

1uF

VDD

PIC8602

PIC8601

COC86

C86

0.01uF

VDD_CLK1

PIL901

250mA

220 ohm

COC87

C87

1uF

PIC8701

PIC8702

PIC8 01

PIC8 02

VDD

COL10

L10

COC88

C88

1uF

PIC8901

PIC8902

C

VDD_PLL34

COL11

L11

PIL1002

PIL1102

PIC9 01

PIC9 02

250mA

220 ohm

COC99

C99

1uF

PIC10101

PIC102 1

COC101

C101

PIC10102

0.01uF

PIC102

PIL1101

250mA

220 ohm

COC102

C102

1uF

PIC10301

PIC10302

PIC10401

COC103

C103

1uF

PIC10402

COC104

C104

0.01uF

0.1uF

Title

D

LMH1983 Eval Board - Power

Pin 10

Size

Number

Revision

B

A

Date:

File:

1

COC89

C89

0.01uF

COC108

C108

PIC108 2

D

Pin 2

COC79

C79

0.01uF

PIC108 1

COC107

C107

PIC10702

PIC7102

10uF

PIC7201

COC71

C71

1uF

COR85

R85

COC74

C74

475

C0G/NP0: 0.01uF

PIC7402

VDD_CLK2

PIL1001

COC106

C106

COC70

C70

PIR8302

VDD_CLK3

PIL601

PIC8101

PIC10 01

COC100

C100

1uF PIC10 02

PIC10601

PIC70 2

PITP30 1

PIC7101

COL8

L8

VDD

COC105

C105

PIC7401

VDD

PIL501

Layout Note: Distribute caps around the 4 sides of

LMH1983 for decoupling the VDD power supply

plane.

PIC105 1

PIC70 1

COL6

L6

250mA

COC76

C76 220 ohm

1uF

2

1

10uF

COC91

C91

10uF

PIC6902

PIR8001

COC69 0

C69

10uF

PIR8501

VDD

PIJ1802 PIJP1801

COC90

C90

PIC7302 1800pF

PIR8002

Note: LDO output voltage

Vout 1V*(1+R_hi/R_lo) = 3.30V

COJP18

JP18

IDD(U1)

PIC9201

PIC9202

3

PIU903

GND

COR83

R83

1.10k

COC73

C73

1

PIC6901

PIR8301

PIU901

LP3878MR-ADJ

VDD_CLK4

PIL502

PIC9101

PIC9102

PIC7301

6

PIU906

BYP

COL5

L5

Layout Note: Pin Legend is

"5V IN" (pin 8)

"N/C" (pin 7)

"LDO 3.3V" (pin 6)

"3.3V" (pin 5)

"GND" (pins 1-4)

PIC90 1

PIC90 2

A

B

VDD

C

3V3

5

PIJ805

POWER

3V3

PIU905

ADJ

COJP17

JP17

LDO ENAB

Layout Note: LED

Legend is "5V IN"

3V3

B

PIJP1701 PIJP1702

PID501

SD

COR80

R80

5

OUT

1

2

2

COD5

D5

8

PIU908

IN

COR84 2

R84

PIU902 NC

10K PIU907

7

NC

PIR8402 PIU909

9

DAP

LG M670-J2M1-1-0-10-R18-Z

PIJ802

COTP30

TP30

3V3

COU9

U9

5V

1

Note: Remove 0R resistor when

applying an external 3.3V power

supply to the 3V3 input.

LDO_3V3

0.34V

348

PIJ801

PID401

2

3

11/3/2009

C:\Projects\..\POWER SUPPLY.SchDoc

Sheet 5of 5

Drawn By:

Sauerwald

4

�1

2

3

4

A

A

VDD

COU10

U10

COP2

P2

COP1

P1

6

5

4

3

2

1

10

11

PIU10011

12

PIU10012

13

PIU10013

14

PIU10014

15

PIU10015

16

PIU10016

17

PIU10017

PIP206

PIU10010

PIP205

PIP204

PIP203

PIP202

PIP201

Header 6

GND

SCL

SDA

B

VDD

PIR8602

COJ9

J9

0.22uF

PID801

1

PISW203

COD7

D7

2

2

4

PISW202

PISW204

COD8

D8

PID802

2

PID702

GND

PD0 (SCL/INT0)

PD1 (SDA/INT1)

PD2 (RXD1/INT2)

PD3 (TXD1/INT3)

PD4 (IC1)

PD5 (XCK1)

PD6 (T1)

PD7 (T0)

2

3

4

PIU1004

5

PIU1005

6

PIU1006

7

PIU1007

8

PIU1008

9

PIU1009

PE7 (INT.7/AIN.1/UVcon)

PF0 (ADC0)

UVcc

PF1 (ADC1)

DPF2 (ADC2)

D+

PF3 (ADC3)

UGnd

PF4 (ADC4/TCK)

UCap

PF5 (ADC5/TMS)

VBus

PF6 (ADC6/TDO)

PE3 (IUID)

PF7 (ADC7/TDI)

33

34

PIU10034

43

PIU10043

18

PIU10018

19

PIU10019

PE0 (WR)

PE1 (RD)

PE2 (ALE / HWB)

PE4

PE5

PIU1003

1

PID701

3

PISW201

PIJ901

PIU10033

HWB

C

20

1

PIU10020

VDD

535-9103-1-ND

PIU1001

COY1

Y1

16 MHz XTAL Osc.

PIY102

PIR8702

COC113

C113

PIC11302 PIC11301

SW3

1 COSW3

PISW301

23

24

PIY101

PIU10023

PIU10024

COR87

R87

47k

PIC1 401

PIR8701

PIC1 402

PIC1 501

COC114

C114

15pF

PIC1 502

PA0 (AD0)

PA1 (AD1)

PA2 (AD2)

PA3 (AD3)

PA4 (AD4)

PA5 (AD5)

PA6 (AD6)

PA7 (AD7)

25

PIU10025

26

PIU10026

27

PIU10027

28

PIU10028

29

PIU10029

30

PIU10030

31

PIU10031

32

PIU10032

PIU1002

1

2

PIJ902

3

PIJ905

PIJ903

4

PIJ906

PIJ904

F2594CT-ND

1-1470156-2

VBUS

DD+

GND

PIR8601

PIC10902 PIC10901

SW2

1 COSW2

COR86

R86

47k

COC109

C109

PB0 (SS)

PB1 (SCK)

PB2 (MOSI)

PB3 (MISO)

PB4 (OC0)

PB5 (OC1A)

PB6 (OC1B)

PB7 (OC2/OC1C)

PC0 (A8)

PC1 (A9)

PC2 (A10

PC3 (A11)

PC4 (A12)

PC5 (A13)

PC6 (A14)

PC7 (A15)

51

50

PIU10050

49

PIU10049

48

PIU10048

47

PIU10047

46

PIU10046

45

PIU10045

44

PIU10044

PIU10051

PIP103

PIP105

PIP107

PIP109

PIP1011

PIP1013

PIP1015

35

PIU10035

36

PIU10036

37

PIU10037

38

PIU10038

39

PIU10039

40

PIU10040

41

PIU10041

42

PIU10042

61

60

59

PIU10059

58

PIU10058

57

PIU10057

56

PIU10056

55

PIU10055

54

PIU10054

1

3

5

7

9

11

13

15

2

4

6

8

10

12

14

16

PIP102

PIP104

PIP106

PIP108

PIP1010

PIP1012

PIP1014

PIP1016

Header 8X2

GND

B

PIU10061

PIU10060

VDD

52

21

64

PIU10064

62

PIU10062

VCC

VCC

AVCC

AREF

PIU10052

GND

GND

GND

PIU10022

RESET

PE6 (INT.6/AIN.0)

PIP101

PIU10021

PIC1 201

PIC1 202

22

53

63

PIU10063

PIU10053

PIC1 0 1

PIC1 0 2

COC110

C110

0.1uF

PIC1 101

PIC1 102

C

COC111

C111

1uF

COC112

C112

0.1uF

XTAL2

XTAL1

AT90USB128/64

COC115

C115

15pF

GND

0.22uF

3

PISW303

GND

2

4

PISW302

PISW304

Title

RESET Interface

D

LMH1983 Eval Board - USB Interface

Size

D

Number

Revision

B

A

GND

Date:

File:

1

2

3

11/3/2009

C:\Projects\..\USB Interface.SchDoc

Sheet 4 of 5

Drawn By: Sauerwald

4

�CODesignator1

COJP17

PAJP1701 PAJP1702

COC74

COU9

PAU901

PAU902

COC68

PAU908

PAU909

PAU904

PAR8501

PAR8502

PAC9001

PAC9002

COTP30

PAC7102

PAC7101

COJP18

PAJP201

PAJP202

PAR302 PAR301

COR3

COJP3

COC2

PATP101 PAC102

PAC9301

PAC9302

PAC9401

PAC9402

COTP28

COTP29 COC42

COC43

PATP3101

PATP2901

PAC202

PAC201

PAC101

PAC801

PAC802

PAL302 PAC1501

PAL301

PAC1502

PAC1701 PAC1601

PAC1702 PAC1602

COC16

COJ2

PASW102

COTP3

COSW1

PATP301

PAR2002

COR20

PAR2001 PAR2003

PAC1401

PAC1402

PAU1014

PAU1013

PAU103

PAU104

PAU105

PAU106

PAU1012

PAU1011

PAU1010

PAU109

PAU107

COR12

COR16

PAR1202 PAR1201

PAR1602 PAR1601

COTP18

COR19

PAR1502 PAR1501

PAX101 PAX102 PAX103

PAR1901

PAR1902

PAJP1302 PAR60 1

PAJP1301 PAR60 2

COJP12

PAJP602

PAC7902

PAC7901

PAU301

PAU302

PAU303

PAU304

PAU305

PAU3041

PAU306

PAU307

PAU308

PAU309

PAU3010

PATP1801

PATP1901

PAJP601

COTP11

PAC2301PAC2302

PAU3025

PAU3024

PAU3023

PAU3022

PAU3021

PATP801

COR40 COR43COR45

PATP2001 PATP2101 PATP2201

COTP23

PAR4301 PAR4501

PAR4302 PAR4502

PAR2702

PAR2701

PATP2301 PATP2401 PATP2501

PATP1201

PAJP1402

PAJP1401

PAR6601

PAR6602

PAR1801 PAR1802

COC18

COR65

PAR6501

PAR6502

PAU6016PAU6015PAU6014 PAU6013

PAU601

PAU602

PAU603

PAU604

PAU6017

COTP14

PATP1401

COTP13

PATP1301

COC58

COC57

PAR2602 PAR2601

COC25 COR26

COTP10

COTP12

PAJP1502

COR72

PAU7016PAU7015PAU7014

PAR7301

PAJP1501 PAR7302

PATP1001

PAU701

PAU702

PAU703

PAU704

PAD201

PAD102

PAD202

PAJP1102

PAJP1101

COP2

PAU7012

PAU7011

PAU7010

PAU709

PAC6202 PAC6201

COD3

PAP206

PAP205

COD1

COD2

PAJP1002

PAJP10 1

PAJP801

PAJP802

COR78

PAJP1602

PAJP1601

PAR7801

PAR7802

COC116

COJP8

COR7

COU8

PAR7701

PAR7702

PAU8016PAU8015PAU8014 PAU8013

PAU801

PAU802

PAU803

PAU804

PAU8017

COSW3

PASW201

PASW203 PASW301

PASW202

PASW204 PASW302

COC67

COC66

PASW303

PAU8012

PAU8011

PAU8010

PAU809

PAC11702 PAC11701

PAR7502

PAR7501

PAC6702 PAC6701

COR75

PAC6602 PAC6601

COC117

PAR8601

PAR8602

COP1

PAP202

PAP102 PAP104 PAP106 PAP108 PAP1010 PAP1012 PAP1014 PAP1016

PAP201

PAP101 PAP103 PAP105 PAP107 PAP109 PAP1011 PAP1013 PAP1015

PAJ903 PAJ904

PAJ906

PAR8701 PAR8702

COR87

COJ9

PAJ902 PAJ901

PASW304

PAP204

PAP203

PAC11602 PAC11601

COR70

PATP901

COSW2

COR86

PAR7002

PAR7001

PAC6302 PAC6301

PAU805PAU806PAU807 PAU80

PAD101

PAJP1103

COJP11

PAR7201

PAR7202

PAU7013

PAU7017

COC63

COC62

COTP9

COJP16

PAD302

COR63

COC119

PAU705PAU706PAU707

PAU706

PAU708

COJP10

PAD301

PAC11902 PAC11901

PAR6302

PAR6301

PAC5702 PAC5701

COR73 COU7

COJP15

PAJP902

PAJP1104

PAU6012

PAU6011

PAU6010

PAU609

COC23

COJP9

COJP5 PAJP501 PAJP502

COJP7

PAC5802 PAC5801

PAJP901

COR18

PAJP701

PAJP903

PASW101

PAC11802 PAC11801

COR57

COC118

PAU605PAU606PAU607 PAU608

COR27

COTP24 COTP25

PAC1801

PAC5202 PAC5201

COR66 COU6

COJP14

PAC2501PAC2502

COC82

PAC8201

PAC8202

COTP20 COTP21 COTP2

PAU5012

PAU5011

PAU5010

PAR5702

PAU509

PAU505PAU506PAU507 PAU508

PAR5701

PAC5302 PAC5301

PAJP702

PATP1101

PAC2101PAC2102

PAU3030

PAU3029

PAU3028

PAU3027

PAU3026

PAU301 PAU3012PAU3013PAU3014PAU30U153P0A1U63P0A1U73P0A1U83P0A1U93020

PAR4001

PAR4002

PAR5901

PAR5902

PAU5013

PAU5017

COJP6

COU3

COC19

PAU504

PAR3701 PAR3702

PAR2102 PAR2101

PAC1902

PAU5016PAU5015PAU5014

PAU501

PAU502

PAU503

COC53

COC52

PAR5201

COR47

COR24 COTP15

COC3 COR4 PPAARR44 0012

COR37

COR25

PATP1601

COC21

COTP17 COC79

PAU304 PAU30 9PAU30 8PAU30 7PAU30U63P0A3U53P0A3U43P0A3U3P0A3U23031

PAR2502 PAR2501

PATP1701

COTP19

COR21

PAR2 02 PAR2301 PAC1901

PAR2 01 PAR2302

COTP8COR2 COR23

PAC1802

PAR1702 PAR1701

COR17

COR5

PAX106 PAX105 PAX104

PAX100

PAR202 PAR201 COR2

PAC301 PAC302 COC3

PAR5601 PAC4801

PAX206 PAR5602 PAC4802 PAR5202 PAJP1201

PAX205 PAR5401 PAR5402 COR54 PAJP1202

PAX204 PAR5501PAR5502 COR55

COX2 PATP2601

COTP26

PATP1501

PAR2401

PAR2402

PAC3301

PAR502 PAR501

PAU108

COR15

COX1

PAC4302 PAC4301

COR60COU5 COR59

PAX200

PAX201

COTP16

COR6

COL3 COC15COC14

COC17

PAJ202 PAJ207

PAJ203 PAJ206

PAJ204 PAJ205

PAR5301 PAR5302

PAU401 PAU406 PAR5101 PAC4701

PAU402 PAU405

PAU403 PAU404 PAR5102 PAC4702

PAC3902 PAR4701PAR4702 PAX202

PAX203

COC39

PAC3302

COC40 PAC40 1 PAC40 2

COR14

COR1

PAR602PAR601

PAR602

PAR601

PAJ201 PAJ208

PAR4901

PAR4902

COR56 COC48 COR52

PAC4202 PAC4201

PATP2701 PAC3901

COTP27

PAR101 PAR102

PAU101

PAU102

COC8

COR53

COR49 COU4 COR51COC47

PAJP301 PAJP302

COU1

COC1

COTP1

COC4

PAC401PAC402

COJP2

PATP2801

COC70 COC71 COC72 PATP3001

COTP5

COC93 COC94 PATP501

PAC7202

PAC7201

PAC9101 PAC9201 PAJP1802 PAJP1801

PAC9102 PAC9202

PAR1401 PAR1402

PATP201

PAC901

PAJ102

PATP701

PATP601

COJP13

COD6

COTP31

PAJP102

COTP7

COTP6

COR82

PAR8202

PAR8201

PATP401

PAJP101

PASW103

PAD601

COJP4

COTP4COC6

PAJP401 PAJP402

PAC602PAC601

PAC602

PAC601

COC5 PAR901 PAR902

PAC502 PAC501

COL1 COR9 PAR1101 PAR1102

PAL102

PAL101

COTP2

COR11

PAC902

PAR402

PAR401

PASW104

PAD602

PAD501

COR83 COC90 COC91 COC92

PAR8302

COJP1 COR4 COC9

PAJ101

PAD502

COR80 PAC7002

PAR8002 PAR8001 PAC7001

PAC6902

PAC6901

PAU905

COR85

COJ8

PAJ103

PAU907

PAC6802 PAU903

PAU906 PAC7302

PAC6801

PAC7301

COD4 PAD402 PAD401 PAR8301

PAJ801 PAJ808

PAJ802 PAJ807

PAJ803 PAJ806

PAJ804 PAJ805

COJ1

COR81

COC73 COC69 COD5

PAR8102

PAR8101

PAC7401 PAC7402

PAJ905

���PAR8401 PAR8402

COR84

COC49

COR50 COR48

PAR5002

PAR5001

PAL402PAL401

PAL402

PAL401

PAC4501 PAC4502

PAC4901 PAC4902

PAR5802

PAR5801

COC50 PAC50 1 PAC50 2

PAC4 01 PAC4402 COC44

COL4

PAR4801

PAR4802

COR58

PAR6102PAR6101

COR61

COC45

PAC4102 PAC4101

COC41

PAC4602

PAC4601

COC46

COR7

COC13 PAC1302PAC1301

COC12 PAC1202 PAC1201

COL2

COC11 PAC1101 PAC1102

COC10 PAC1001 PAC1002

COC7

PAU2016

PAU2015

PAU2014

PAU2013

COR29

PAU2012

PAU2011

PAU2010

PAU209

PAU205

PAU206

PAU207

PAU208

COU2

COR33 COC75

PAR2901PAR2902

PAR2901

PAR2902

PAU201

PAU202

PAU203

PAU204

COR30

PAR3302 PAR3301

COR34

PAR3001PAR3002

PAR3001

PAR3002

PAR3402 PAR3401

COR31

COR35

PAR3102 PAR3101

PAR3502 PAR3501

COR32

PAR802 PAR801

PAC2802 PAC2801

CO 106

PAR3602 PAR3601

COR36

COC31

COC28

PAR1002 PAR1001

PAC10602 PAC10601

PAC10502 PAC10501

COC105

PAR3202 PAR3201

COR8

COR10

COC98

PAR1302 PAR1301

PAR3802

COR39 PAR3801

PAR3902 PAR3901

PAC3502 PAC3501

PAR4202

PAR4201

PAC3102

PAC3101

COC101

COC108

PAC10802

PAC10701 PAC10801

COC81

PAC8102PAC8101

PAC8102

PAC8101

PAL502 PAL501

COC107 COC76 COC104

PAC8302

PAC8301

PAC10301

PAC10302

PAC9802

PAC3801

PAC3802

PAC3701 PAC3601

PAC3702 PAC3602

PAC3001

PAC3002

COL9

COC86

COC83

PAL1 01

PAL1 02

COR42

PAC8502

PAC8501

PAC9601

COL8

PAC8402

PAL801PAL802 PAC8401

COC84

COC54

PAC5401 PAC5402

COC56

PAC5601 PAC5602

PAR6402

PAR6401

COR64

PAR6702PAR6701

COR67

COC27

COC20

PAC2201PAC2202

PAC2201

PAC2202 COC22

COC24

PAC2401PAC2402

PAC2401

PAC2402 PAC2901 PAC2902

COC29

PAC7701

PAL602PAL601

PAL602

PAL601

COL6

PAC7702 PAC8002 PAC8001

COC80

PAC10201

COC60 PAC60 1 PAC60 2

PAC10202

PAC9701

PAC2001PAC2002

PAC2701 PAC2702

COL11 COC7

PAR2802

PAR2801

COC102

COC38 COC37 COC36COC30 COR28 COC103

PAC9702

COC61

PAC6101 PAC6102

COC97

PAR7102

PAR7101

COR71

PAR7402PAR7401

COR74

COR41

PAR4102PAR4101 PAC3201

PAC3401PAC3402

PAC3401

PAC3402 PAC3202

COC32

PAR6901

PAR6201

PAR6801

PAR6902

PAR6202

PAR6802

COR69 COR62 COR68

PAC5902

PAC5901

COR46

PAL901 PAL902

PAC8902 PAC8901 PAC8602

COC89 PAC8601

PAC7601 COL5 PAC10401

PAC7602

PAC10402

COC35 COC34

PAR4601 PAR4602

PAC8702

PAC8701

PAC8802

PAC8801

PAC10102 PAC10101

PAC10702

PAC9801

COR13

COR38

PAC10002PAC10001 PAL10 1 PAC9902

PAL10 2 PAC9901

PAC7502PAC7501 PAC7802

COL7 PAL701 PAL702 PAC7801

COC96

PAC9602

PAC2602

PAC2601

COC100

COC95 PAC9502PAC9501

PAL202PAL201

PAL202

PAL201

PAC702 PAC701

COC26

COC87

COC85

COC78 COL10 COC9 COC8

PAR701 PAR702

COC59

PAC5102

PAC5101

COC51

COC111

PAC11101 PAC11102

COC110

PAC11001 PAC11002

COC112COC64

PAC11201 PAC11202 COC65

PAC6401 PAC6402

PAU10048

COC5

COC109

PAU1001

PAU10047

PAU10046

PAU10045

PAU10044

PAU10043

PAU10042

PAU10041

PAC10901 PAU10040

PAU10039

PAC10902

PAU1002

PAU1004

PAU1005

PAU1006

PAU1007

PAU1008

PAU1009

PAU10010

PAU1003

PAU10038

PAU10011

PAU10037

PAU10036

PAU10012

PAU10013

PAU10035

COD8 COR79

PAD701

PAD702

COD7

PAU10015

PAU10033

PAU10016

COU10 PAU10 32PAU10 31PAU10 30PAU10 29PAU10 28PAU10 27PAU10 26PAU10 25PAU10 24PAU10 23 PAU10 2 PAU10 21 PAU10 20PAU10 19 PAU10 18PAU10 17

COY1

COC114

PAC11301PAC11302

PAC11301

PAC11302

COC113

PAY102 PAY101

PAC11402 PAC11401

PAC11501 PAC11502

PAR7902 PAR7901

PAD802

PAD801

PAU10014

PAU10034

PAR7602

PAR7601

PAC6501 PAC6502

PAU10 49PAU10 5 PAU10 51PAU10 52PAU10 53PAU10 54PAU10 5 PAU10 56PAU10 57PAU10 58 PAU10 59PAU10 6 PAU10 61PAU10 62 PAU10 63PAU10 64

PAC5502

PAC5501

COC115

COR76

�CODesignator1

COJP17

PAJP1701 PAJP1702

COC74

COR81

COC73 COC69 COD5

COR84

PAC7401 PAC7402

COU9

PAU901

PAU902

COC68

PAR8102

PAR8101

PAD602

PAD501

PAD601

COTP6

COR82

PAR8202

PAR8201

PAU909

PAU907

PAU904

PAU905

COR83 COC90 COC91 COC92

PAR8302

COR85

COR80 PAC7002

PAR8002 PAR8001 PAC7001

PAC6902

PAC6901

PATP601

PAR8501

PAR8502

PAC9001

PAC9002

COTP30

PATP2801

COC70 COC71 COC72 PATP3001

COTP5

COJP18

COC93 COC94 PATP501

PAC7102

PAC7101

PAC7202

PAC7201

PAC9101 PAC9201 PAJP1802 PAJP1801

PAC9102 PAC9202

PAC9301

PAC9401

PAC9402

PAC9302

COJP3

COTP28

COR50 COR48

COR53

COR49 COU4 COR51COC47

PAJP301 PAJP302

PATP2901

PAC4501 PAC4502

PAJP1302 PAR60 1

COC50 PAC50 1 PAC50 2 PAJP1301 PAR60 2

COC41

PAC4302

PAC4301

PAU5016PAU5015PAU5014

PAC4901 PAC4902

COR61

COC45

COR56 COC48 COR52

PAC4202 PAC4101

PAC4102

PAC4201

PAU501

PAU502

PAU503

PAU504

PAR6102PAR6101

PAR5601 PAC4801

PAR5201

PAX206 PAR5602 PAC4802 PAR5202 PAJP1201

PAX205 PAR5401 PAR5402 COR54 PAJP1202

PAX204 PAR5501PAR5502 COR55

COX2 PATP2601

COTP26PAC9602

PATP1501

PAC9601

COC95

PAR101 PAR102

COJP2

PAC40 1 PAC40 2 COC26

COC87

COC85

COC78COR47 COL10COR4 COC9 COCRO2C48

PAR1401 PAR1402

PATP201

PAC901

PAL202PAL201

PAL202

PAL201

COC2

PAC702 PAC101

PAC102

PAC701

PAU101

PAU102

PAU1014

PAU1013

PAU103

PAU104

PAU105

PAU106

PAU1012

PAU1011

PAU1010

PAU109

PAU107

PAU108

PAU2016

PAU2015

PAU2014

PAU2013

PATP1601

PAU201

PAU202

PAU203

PAU204

PAU2012

PAU2011

PAU2010

PAU209

CO 106

PAU205

PAU206

PAU207

PAU208

COR19

COC16

COC98

COR40 COR43COR45

PAJP602

PAJP601

PAJP702

PAR2002

COR20

PAR2001 PAR2003

COR38

PAC1801

COC18

PAJP902

PASW101

PAJP901

COTP7

COR18

PATP701

COJP5 PAJP501 PAJP502

PAR3802

PAR3801

PAJP903COR39

PAR3902 PAR3901

PAR1801 PAR1802

PAC3502 PAC3501

PAR4202

PAR4201

PAJP701

COC32

PAJP1104

PAD301

PAC5902

PAC5901PAD302

PAJP1103

PAR4601 PAR4602

PAJP1101 COR46

COJP11

PAP206

COP2 PAP205

COJ3

PAJ303

PAJ302

PAJ305 PAJ301 PAJ304

PAC5102

PAC5101

COC59

COC51

COD3

COD1

COC84

PAR6901

PAR6201

PAR6801

PAR6902

PAR6202

PAR6802

PAD101

PAD102

PAR6501

PAR6502

PAU6017

PAU6012

COJ5

PAR6402

PAR6302

PAR6401

PAR6301

PAU605PAU606PAU607 PAU608

PAJ502

PAJ504

COR64

COR63 PAJ503 PAJ505

PAC11902 PAC11901 PAJ501

PAU6011

PAU6010

PAU609

PAC5801

PAC5701

COC82

COJP15

PAC11101 PAC11102

COC110

PAC11001 PAC11002

PAC5502

PAC5501PAD202

COR86

COC5

PAU704

PAJP1002

PAC11201 PAC11202

COC65

PAU1001

PAU10046

PAU1003

PAU10044

PAU1005

PAU1006

PAU1007

PAU1008

PAU1009

PAU10010

PAU10037

PAU10036

PAU10012

PAU10013

PASW204 PASW302

PASW304

PAU10033

PAP102 PAP104 PAP106 PAP108 PAP1010 PAP1012 PAP1014 PAP1016

PAP101 PAP103 PAP105 PAP107 PAP109 PAP1011 PAP1013 PAP1015

COJP16

COR78

PAC6401 PAC6402

PAJP1602

PAC6501 PAC6502

PAJP1601

PAR7801

PAR7802

PAR7002

PAR7102

PAR7101

PAR7001

PAC6301

PAC6201

PAU801

PAU8017

PAR7902 PAR7901

COD8 COR79COC67

PAD701

PAD702

COD7

COC66

PAU8012

PAC11501 PAC11502

COC115

PAJ704

PAC11702 PAC11701 PAJ701

PAC6702 PAC6701

COR76

COR75 PAJ703 PAJ705

PAC6602 PAC6601

COC117

PAU8011

PAU8010

PAU809

PAR7502

PAR7602

PAR7601

PAR7501

COJ9

PAJ903 PAJ904

PAY102 PAY101

PAC11402 PAC11401

COJ7

PAJ702

PAR7701

PAR7702

PAJ902 PAJ901

PAJ906

COR71

COR70 PAJ603 PAJ605

COR7

PAU8016PAU8015PAU8014 PAU8013

PAU802

PAU803

PAU804

PAJ604

COC116

COU8

PAD802

PAD801

PAC11301PAC11302

PAC11301

PAR8701PAC11302

PAR8702

COR87

COC113

PAJ602

PAC11602 PAC11601 PAJ601

COJP8

PAU805PAU806PAU807 PAU80

PAU10015

PAU10016

COY1

COC114

PAJP801

PAJP802

PAU10014

COU10 PAU10 32PAU10 31PAU10 30PAU10 29PAU10 28PAU10 27PAU10 26PAU10 25PAU10 24PAU10 23 PAU10 2 PAU10 21 PAU10 20PAU10 19 PAU10 18PAU10 17

PAP201

PAU709

PAU10011

COP1

PAP202

PAJP10 1

COC112COC64

PAU10048

PASW202

PAU7017

PAU7012

PAU7011

PAU7010

PAU705PAU706PAU707

PAU706

PAU708

PAU10043

PAU10042

PAU10041

PAC10901 PAU10040

PAR8601

PAR8602 PAU10039

PAU10038

PAC10902

PAU10034

PAR7201

PAR7202

PAU7013

PATP1001

PAU10 49PAU10 5 PAU10 51PAU10 52PAU10 53PAU10 54PAU10 5 PAU10 56PAU1COSW3

0 57PAU10 58 PAU10 59PAU10 6 PAU10 61PAU10 62 PAU10 63PAU10 64

COSW2

PAU10047

PAU1002

PASW201

PASW203 PASW301

PASW303 PAU1004

PAU10045

PAU10035

PAU7016PAU7015PAU7014

PAU701

PAU702

PAU703

COJ6

COR72

COR73

COL11 COC7

COC111

PAD201

COD2

COC119

COC86

COC83

COC109

PAP204

PAP203

COJP14

PAU601

PAU602

PAU603

PAU604

PAU3024

COR69 COR62 COR68

COJP9

PAJP1102

COC108 PAU3041

COC107 COC76 COC104

COC35 COC34

COC118

COJP7

COR65

COR66

COR41

PAR4102PAR4101 PAC3201

PAC3401PAC3402

PAC3401

PAC3402 PAC3202

COR5C7OR58PAJ403 PAJ405

PAC5202 PAC5201

COJP6

COC96

COR27

COC102 COC97

COC38 COC37 COC36COC30 COR28 COC103

COR42 COTP23 PATP2301 PATP2401 PATP2501 PATP1201 COTP12 PATP901 COJP10

COTP20 COTP21 COTP2

PATP801

COSW1

PASW103

COC19

COR2 COR23

PASW102

PAJ404

PAC11802 PAC11801 PAJ401

PAL901 PAL902

PAU3030

PAU3029

PAU3028

PAU3027

PAU3026

PAL502 PAL501

COC31

PAL301

COC101

PAU301

PAU302

PAU303

PAU304

PAU305

PAU307

COC15COC14

COC17

PASW104

COC3

COC79

PAU5012

PAU5011

PAU5010

PAR5802

PAR5702

PAU509

PAU505PAU506PAU507 PAU508

PAR5801

PAR5701

PAC5302 PAC5301

COR7 PAR701 PAR702

COC39

COTP11 PATP1101

PAC3302

COU6

COC13 PAC1302PAC1301

COC40

COR14

PAR2401

PAC2602

COC100

COC54 PAC5401 PAC5402 PAJP1402 PAR6601 PAU6016PAU6015PAU6014 PAU6013

PAC9502

COR1

COC12 PAC1202 PAC1201

PAC3301 PAC2601

PAR2402

COC4

COTP15

PAR6602

PAC9501

PAC401PAC402

PAJP101

PAJP201

COL2

COC56 PAC5601 PAC5602 PAJP1401

PAC8702

PAJ103

COTP16

PAR4 01 PAC9902 PAC8802 PAC8701

COC11 PAC1101 PAC1102

PAJP102

PAJP202

COU1

COR29 COR33 COC75 PAC10002PAC10001 PPPAAALL11R00 412 02 PAC9901 PAR3701 PAR3702

PAC8502 COL8 PAC8402

PAR6702

PAR6701

PAC5802

COR67

COC10 PAC1001 PAC1002

PAC202

PAC8801 COR37

COL9 PAC8501 PAL801PAL802

COR25

COC58 PAC5702

PAR2901PAR2902

PAR2901

PAR2902

PAR3302 PAR3301

PAC8401

PAR202 PAR201 COR2

PAC7502PAC7501 PAC7802

PAC7902

COC21

PAC201

PAR1202 PAR1201

COR12COR30

COR34

COTP14 PATP1401

PAC10102 PAC10101

COTP17

COL7 PAL701 PAL702 PAC7801

PAU304 PAU30 9PAU30 8PAU30 7PAC8902

PAU30U63P0A3U53P0A3U43PPAC8901

0A3U3P0A3U23031PAC8602

PARC257021 PACR275021 COC27

COC57

PAR302 PAR301 PATP101

PAC301 PAC302 COC3

PAC7901

PAC2001

PAJ101

PAC2101PAC2002

PAC2102

PAR3001PAR3002

PAR3001

PAR3002 PATP1701 PAR3402 PAR3401

PAR1601

COR16 PAR1602

PAC801

PAR1702 PAR1701

COR3

COC89 PAC8601

COC20

PAR502 PAR501

PAC10602 PAC10601

COR31

COR35

COC22

COC1

PAC2201PAC2202

PAC2301

PAC2201

PAC2302

PAC2202

COTP1 COC7

COC23

PAC802

PAU306

PAU3025

PAC10502 PAC10501

COR17

PAC10802

COC24

PAR602PAR601

PAR602

PAR601

PAR3102 PAR3101

PAR3502 PAR3501

PAU308

PAU3023

COR5

PAU309 COC81PAU3022

PAC2501

PAC2502

COU2 COTP18 PATP1801

PAU3021

PAC2401PAC2402

PAC2401

PAC2402 PAC2901

PAJ102

PAC10701 PAU3010

PAC10801 PAU301 PPAC8102

COC29

PAC8102PAC8101

PAR2602 PAC2902

PAR2601

COC8

COR6

COR32

COC105

AU3012PAU3013PAU3014PPAC8101

AU30U153P0A1U63P0A1U73P0A1U83P0A1U93020 PAC8302

COTP13 PATP1301

COC25

PAR3202 PAR3201 PATP1901 PAR3602 PAR3601

PAC3102

PAC10702

PAC8301

PAC7701

PAL602PAL601

PAL602

PAL601 COR26

COL6

COR8

COR15

PAC3101

PAC7601 COL5PAC8201PAC10401 PAC10301 PAL1 01 PAC7702 PAC8002 PAC8001

COTP19

PAC2802 PAC2801

COR36

COC80

PAJ201 PAJ208 PAR802 PAR801

PAR1502 PAR1501 PAR1901 COR21

PAC7602

PAL1 02 PAC10201

COL3

COU7

COX1

PAC8202

PAC10402

PAC10302

COC28

COU3

PAC9801

COC60 PAC60 1 PAC60 2 PAJP1502 PAR7301

PAC10202

PAJ202 PAJ207 PAR1002 PAR1001 COR10 PAL302 PAC1501 PAC1401 PAX106 PAX105 PAX104 PAR1902 PAR2102 PAR2101

PAC9701

PAC9802

PAR2 02 PAR2301 PAC1901

PAC1502 PAC1402

PAC9702

COC61 PAC6101 PAC6102 PAJP1501 PAR7302

PAR4001 PAC3701

PAC3801

PAR4301 PAC3601

PAR4501

PAR2702 PAR2802