EVALUATION KIT AVAILABLE

MAX20733

Integrated, Step-Down Switching Regulator

General Description

The MAX20733 is a fully integrated, highly efficient

switching regulator for applications operating from 4.5V to

16V and requiring up to 35A maximum load. This singlechip regulator provides extremely compact, high-efficiency power-delivery solutions with high-precision output

voltages and excellent transient response for networking,

datacom, and telecom equipment.

The IC offers a broad range of programmable features

through capacitors and resistors connected to dedicated

programming pins. Using this feature, the operation can

be optimized for a specific application, reducing the

component count- and/or setting-appropriate trade-offs

between the regulator's performance and system cost.

Ease of programming enables using the same design for

multiple applications.

The MAX20733 includes protection capabilities. Positive

and negative cycle-by-cycle overcurrent protection and

overtemperature protection ensure a rugged design. Input

undervoltage lockout shuts down the device to prevent

operation when the input voltage is out of specification. A

status pin provides an output signal to show that the output voltage is within range and the system is regulating.

Benefits and Features

●●

High Power Density and Low Component Count

• Overall Solution Size: 509mm2 Including Inductor

and Output Capacitors

• 90.8% Peak Efficiency: VDDH = 12V and

VOUT = 1V

• Fast Transient Response: Supports Up to 300A/μs

Load Step Transients

●●

Optimized Component Performance and Efficiency

with Reduced Design-In Time

●●

Increased Power-Supply Reliability with System and

IC Self-Protection Features

• Differential Remote Sense with Open-Circuit

Detection

• Hiccup Overcurrent Protection

• Programmable Thermal Shutdown

Typical System Efficiency vs.

Load Current (VDDH = 12V)

100

95

●●

Communications Equipment

90

●●

Networking Equipment

85

●●

Servers and Storage Equipment

●●

Point-of-Load Voltage Regulators

●●

μP Chipsets

●●

Memory VDDQ

●●

I/O

DESCRIPTION

EFFICIENCY (%)

Applications

75

VOUT

Vout

= 5V= 5V

70

VOUT

= 3.3V

Vout

= 3.3V

VOUT

= 1.8V

Vout

= 1.8V

65

Vout

= 1.2V

VOUT

= 1.2V

Vout

= 1V= 1V

VOUT

60

CURRENT

RATING*

INPUT

VOLTAGE

OUTPUT

VOLTAGE

Electrical rating

35A

4.5V to 16V

0.6484V

to 5.5V

Thermal rating,

TA = 55°C, 200LFM

34A

12V

1V

Thermal rating,

TA = 85°C, 0LFM

22A

12V

1V

*For specific operating conditions, refer to the SOA curves in

the Typical Operating Characteristics section.

19-8604; Rev 0; 10/16

80

Vout

= 0.8V

VOUT

= 0.8V

Vout

= 0.65V

VOUT

= 0.65V

55

50

0

5

10

15

20

IOUT (A)

25

30

Ordering Information appears at end of data sheet.

35

�MAX20733

Integrated, Step-Down Switching Regulator

Absolute Maximum Ratings

Input Pin Voltage (VDDH) (Note 1).........................-0.3V to +18V

VCC...........................................................................-0.3V to +2V

STAT and OE Pin Voltages......................................-0.3V to +4V

PGM1, PGM2, PGM3, VSENSE+ and VSENSEPin Voltages..........................................................-0.3V to +2V

Switching Node Voltage (VX) DC...........................-0.3V to +18V

Switching Node Voltage (VX) 25ns (Note 2)...........-10V to +23V

(BST - VX) Pin Differential...................................... -0.3 to +2.5V

Junction Temperature (TJ)................................................+150°C

Storage Temperature Range............................. -65°C to +150°C

Peak Reflow Temperature Lead-Free.............................. +260°C

Stresses beyond those listed under “Absolute Maximum Ratings” may cause permanent damage to the device. These are stress ratings only; functional operation of the device at these or any

other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device

reliability.

Operating Ratings

Input Voltage (VDDH)................................................. 4.5V to 16V

Junction Temperature (TJ)................................ -40°C to +125°C

Maximum Average Input Current (IVDDH) (Note 3)..................6A

Maximum Average Output Current (IOUT).............................35A

Peak Output Current (IPK)......................................................60A

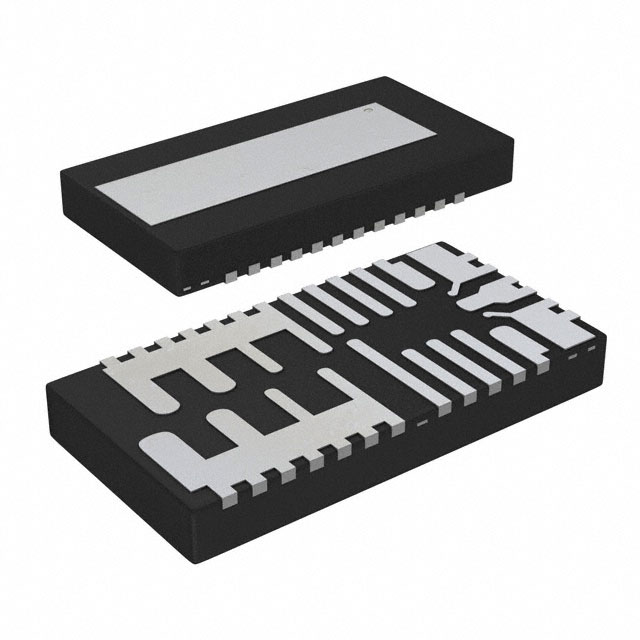

Package Information

PACKAGE CODE

P154A8F+

Outline Number

21-100031

Land Pattern Number

90-100022

THERMAL RESISTANCE, FOUR-LAYER BOARD

Junction to Ambient (θJA)

(Still Air, No Heatsink; Note 4)

13°C/W

Junction to Case (θJC)

0.47°C/W

For the latest package outline information and land patterns (footprints), go to www.maximintegrated.com/packages. Note that a “+”,

“#”, or “-” in the package code indicates RoHS status only. Package drawings may show a different suffix character, but the drawing

pertains to the package regardless of RoHS status.

Note 1: As measured at the VDDH pin referenced to GND pin immediately adjacent using a high frequency scope probe with ILOAD

at IMAX. A high-frequency input bypass capacitor must be located less than 60 mils from the VDDH pin per our design

guidelines.

Note 2: The 25ns rating is the allowable voltage on the VX node in excess of the -0.3V to +18V DC ratings. The VX voltage can

exceed the DC rating in either the positive or negative direction for up to 25ns per cycle.

Note 3: See the Average Input Current Limit section.

Note 4: Data taken using Maxim’s evaluation kit, MAX20733EVKIT#. The PCB has four layers of 2oz copper.

www.maximintegrated.com

Maxim Integrated │ 2

�MAX20733

Integrated, Step-Down Switching Regulator

Electrical Characteristics

(Circuit of Figure 6, VDDH = 4.5V to 16V, unless otherwise specified. Typical values are at TA = +32°C. All devices 100% tested at room

temperature. Limits over temperature guaranteed by design.)

PARAMETER

SYMBOL

CONDITIONS

MIN

TYP

MAX

UNITS

SUPPLY VOLTAGE

Supply Voltage Range

VDDH

(Note 5)

4.5

16

V

VOUT

(Note 5)

0.65

5.5

V

OUTPUT VOLTAGE (NOTE 6)

Output Voltage Range

VREF

0.6484

VREF Values

VREF

Selected by C_SEL1 (Note 7)

0.8984

V

1.0

Referred to VSENSE

pins (Notes 5, 8)

VREF Tolerance

0.6484V VREF

-1.2

+1.2

0.8984V VREF

-1.0

+1.0

1V VREF

-1.0

+1.0

%

FEEDBACK LOOP

Integrator Recovery Time

Constant

Gain (see Control Loop section

for details)

tREC

RGAIN

20

Selected by R_SEL3 (Notes 5, 7, 8, 9)

µs

0.72

0.9

1.1

1.4

1.8

2.2

2.9

3.6

4.4

mV/A

SWITCHING FREQUENCY

400

500

Switching Frequency

fSW

600

Selected by C_SEL2 and C_SEL3

(see Tables 5, 6) (Note 7)

kHz

700

800

900

Switching Frequency Accuracy

(Notes 5, 8, 9)

-20

+20

%

INPUT PROTECTION

Rising VDDH UVLO Threshold

(Note 5)

Falling VDDH UVLO Threshold

VDDH_UVLO (Note 5)

4.25

3.7

Hysteresis

4.47

3.9

350

V

mV

OUTPUT VOLTAGE PROTECTION (OVP)

Overvoltage Protection Rising

Threshold

OVP

Relative to programmed VOUT

9.5

OVP Deglitch Filter Time

Power Good Deglitch Filter Time

www.maximintegrated.com

16.5

8

Power Good Protection Falling

Threshold

Power Good Protection Rising

Threshold

13

Relative to programmed VOUT

PWRGD

%

µs

6

9

12

%

3

6

9

%

8

µs

Maxim Integrated │ 3

�MAX20733

Integrated, Step-Down Switching Regulator

Electrical Characteristics (continued)

(Circuit of Figure 6, VDDH = 4.5V to 16V, unless otherwise specified. Typical values are at TA = +32°C. All devices 100% tested at room

temperature. Limits over temperature guaranteed by design.)

PARAMETER

SYMBOL

CONDITIONS

MIN

TYP

MAX

Setting 0

11.8

18.9

26.0

Setting 1

16.0

24.1

32.2

Setting 2

19.8

29.2

38.6

Setting 3

24.5

34.1

43.8

UNITS

OVERCURRENT PROTECTION (OCP)

Positive OCP Inception

Threshold (Inductor Valley

Current)

OCP

Selected by R_

SEL3

(Notes 5, 7, 8, 9)

Hysteresis of Positive OCP

20

Negative OCP Inception

Threshold (Inductor Valley

Current)

Selected by

R_SEL3

Setting 0

-26.4

Setting 1

-31.3

Setting 2

-36.0

Setting 3

-40.8

Hysteresis of Negative OCP

A

%

A

0

%

OVERTEMPERATURE PROTECTION (OTP)

OTP Inception Threshold

OTP

Selected by R_SEL2 (Notes 7, 8, 9)

120

130

140

140

150

160

Hysteresis

10

°C

°C

OE MAXIMUM VOLTAGE

OE Max Voltage

Rising Threshold

Hysteresis

3.6

OE

Measured at OE pin (Note 5)

OE Pin Input Resistance

0.83

(Note 9)

0.97

0.2

200

OE Deglitch Filter Time

0.9

275

0.9

V

V

350

kΩ

2.2

µs

STARTUP TIMING

Enable Time from OE Rise to

Start of BST Charge

tOE

After tINIT

Soft-Start Ramp Time

tSS

Set by R_SEL1 (Note 7)

BST Charging Time

tBST

www.maximintegrated.com

16

µs

1.5

ms

3

ms

8

µs

Maxim Integrated │ 4

�MAX20733

Integrated, Step-Down Switching Regulator

Electrical Characteristics (continued)

(Circuit of Figure 6, VDDH = 4.5V to 16V, unless otherwise specified. Typical values are at TA = +32°C. All devices 100% tested at room

temperature. Limits over temperature guaranteed by design.)

PARAMETER

SYMBOL

Allowable Pullup Voltage

VOHSTAT

CONDITIONS

MIN

TYP

MAX

UNITS

3.6

V

STAT PIN

Status Output Low

VOLSTAT

Status Output High Leakage

Current

Time from VOUT Ramp

Completion to STAT Pin Released

ISTAT = 2.5mA

0.4

ISTAT = 0.2mA, 0V < VCC < UVLO and

0V < VDDH < UVLO (Note 5)

0.65

ISTAT = 1.3mA, 0V < VCC < UVLO and

0V < VDDH < UVLO (Note 5)

0.75

STAT pulled up to 3.3V through 20kΩ

tSTAT

7

125

STAT output low to high, set by R_SEL2

(Note 7)

V

µA

µs

2000

PGM1–PGM3 PINS (ALSO SEE TABLES 2–7)

Allowable R_SEL Resistor Range

12 resistor values detected

R_SEL Resistor Required

Accuracy

EIA standard resistor values only

Allowable C_SEL Capacitor

Range

Three options (0, 220, or 1000pF)

C_SEL Capacitor Required

Accuracy

Use X7R or better

Allowable External Capacitance

Load and stray capacitance in addition

to C_SEL1/2/3

1.78

162

±1

0

kΩ

%

1000

±20

pF

%

20

pF

SYSTEM SPECIFICATIONS (NOTE 10)

Line Regulation

Load Regulation (Static)

Efficiency (VDDH = 12V,

VOUT = 1V)

VOUT

η

±0.2

IOUT = 0 - IMAX

±0.7

Peak

90.8

Full load (35A)

84

%

%

Note 5: Specification applies over the temperature range of TJ = -40° to +125°C.

Note 6: For proper regulation, it is required that VDDH > (VOUT + 2V). If VOUT is set greater than (UVLO - 2V), the IC can come out

of UVLO, but regulation is not guaranteed while VDDH is below (VOUT + 2V). To avoid this condition, OE can be held low

until VDDH is greater than (VOUT + 2V).

Note 7: Parameters that are programmable.

Note 8: Min/max limits are ≥ 4σ about the mean.

Note 9: Guaranteed by design; not production tested.

Note 10: These specifications refer to the operation of the system and are based on the circuit shown in the reference schematic.

Tolerance of external components can affect these parameters. System performance numbers are measured using the

Maxim evaluation board for this product with BOM as shown on the MAX20733 EV kit data sheet. If a different PCB layout

and different external components are used, these values can change.

www.maximintegrated.com

Maxim Integrated │ 5

�MAX20733

Integrated, Step-Down Switching Regulator

Typical Operating Characteristics

(Unless otherwise noted: Tested on the MAX20733EVKIT# with component values per Table 8; VDDH = 12V, VOUT = 1V, fSW = 400kHz,

TA = 25°C, Still Air, No Heatsink.)

STARTUP RESPONSE

TRANSIENT RESPONSE

toc01

toc02

IOUT (10A/div)

VX (20V/div)

VOUT (20mV/div)

STAT(2V/div)

VX (10V/div)

OE (2V/div)

VOUT (200mV/div)

TIME: 100µs/div

CONDITIONS: IOUT = 20A to 30A STEP at 1A/µs

TIME: 500µs/div

TYPICAL VOUT RIPPLE

toc03

VOUT (20mV/div)

VX (10V/div)

TIME: 2µs/div

CONDITIONS: IOUT = 35A

www.maximintegrated.com

Maxim Integrated │ 6

�MAX20733

Integrated, Step-Down Switching Regulator

Typical Operating Characteristics (continued)

(Unless otherwise noted: Tested on the MAX20733EVKIT# with component values per Table 8; VDDH = 12V, VOUT = 1V, fSW = 400kHz,

TA = 25°C, Still Air, No Heatsink.)

SYSTEM EFFICIENCY vs. OUTPUT LOAD

100

LOAD REGULATION

toc04

0.4

95

75

VOUT

Vout

= 5V= 5V

Vout

= 3.3V

VOUT

= 3.3V

70

60

5

10

15

20

IOUT (A)

25

30

JUNCTION TEMPERATURE

vs. SYSTEM POWER DISSIPATION

120

VOUT = 0.65V

.65V

0.1

0.0

-0.3

Vout

= 0.65V

= 0.65V

VOUT

0

1VVOUT = 1V

-0.2

Vout

= 1V= 1V

VOUT

Vout

= 0.8V

VOUT

= 0.8V

55

VOUT = 1.8V

1.8V

-0.1

VOUT

= 1.8V

Vout

= 1.8V

Vout

= 1.2V

VOUT

= 1.2V

65

-0.4

35

0

5

80

60

40

20

15

20

25

30

SYSTEM POWER DISSIPATION

toc06

SLOPE = 13°C/W

10

35

IOUT (A)

toc07

9

8

100

JUNCTION TEMPERATURE (°C)

LOAD REGULATION (%)

80

0

VOUT = 3.3V

3.3V

0.2

SYSTEM POWER DISSIPATION (W)

EFFICIENCY (%)

85

50

VOUT = 5.5V

5.5V

0.3

90

toc05

VOUT

Vout

= 5V= 5V

Vout

= 3.3V

VOUT

= 3.3V

7

Vout

= 1.8V

VOUT

= 1.8V

Vout

= 1.2V

VOUT

= 1.2V

6

Vout

= 1V= 1V

VOUT

Vout

= 0.8V

VOUT

= 0.8V

5

Vout

= 0.65V

VOUT

= 0.65V

4

3

2

1

0

1

2

3

4

5

SYSTEM POWER DISSIPATION (W)

www.maximintegrated.com

6

0

0

5

10

15

20

25

30

35

IOUT (A)

Maxim Integrated │ 7

�MAX20733

Integrated, Step-Down Switching Regulator

Typical Operating Characteristics (continued)

(Unless otherwise noted: Tested on the MAX20733EVKIT# with component values per Table 8; VDDH = 12V, VOUT = 1V, fSW = 400kHz,

TA = 25°C, Still Air, No Heatsink.)

SAFE OPERATING AREA (SOA)

35

35

30

30

25

25

20

15

Vout=0.8V

VOUT = 0.8V

Vout=1.2V

VOUT = 1.2V

5

VOUT = 5.0V

Vout=5.0V

30

40

0

50

60

70

80

90

100

TA (°C)

CONDITIONS: 400LFM

CURVE INDICATES TJ = 125°C, IOUT = IMAX, or IVDDH = IVDDH_MAX,

WHICHEVER HAPPENS FIRST

SAFE OPERATING AREA (SOA)

40

VOUT = 5.0V

Vout=5.0V

60

70

80

90

100

TA (°C)

CONDITIONS: 200LFM

CURVE INDICATES TJ = 125°C, IOUT = IMAX, or IVDDH = IVDDH_MAX,

WHICHEVER HAPPENS FIRST

toc10

30

40

50

SYSTEM EFFICIENCY

vs. OUTPUT LOAD (VDDH = 5V)

100

toc11

95

35

90

30

85

EFFICIENCY (%)

25

IOUT (A)

Vout=0.8V

VOUT = 0.8V

Vout=1.2V

VOUT = 1.2V

Vout=3.3V

VOUT = 3.3V

10

VOUT = 3.3V

Vout=3.3V

5

20

15

Vout=0.8V

VOUT = 0.8V

Vout=1.2V

VOUT = 1.2V

Vout=3.3V

VOUT = 3.3V

10

5

0

20

15

10

0

toc09

40

IOUT (A)

IOUT (A)

40

SAFE OPERATING AREA (SOA)

toc08

Vout=5.0V

VOUT = 5.0V

30

40

50

60

70

80

90

100

TA (°C)

CONDITIONS: STILL AIR / NO HEATSINK

CURVE INDICATES TJ = 125°C, IOUT = IMAX, or IVDDH = IVDDH_MAX,

WHICHEVER HAPPENS FIRST

www.maximintegrated.com

80

75

70

Vout

= 1.8V

VOUT

= 1.8V

Vout

= 1.2V

VOUT

= 1.2V

Vout

= 1V= 1V

VOUT

Vout

= 0.8V

VOUT

= 0.8V

Vout

= 0.65V

VOUT

= 0.65V

65

60

55

50

0

5

10

15

20

IOUT (A)

25

30

35

Maxim Integrated │ 8

�MAX20733

Integrated, Step-Down Switching Regulator

Typical Operating Characteristics (continued)

(Unless otherwise noted: Tested on the MAX20733EVKIT# with component values per Table 8; VDDH = 12V, VOUT = 1V, fSW = 400kHz,

TA = 25°C, Still Air, No Heatsink.)

SYSTEM POWER DISSIPATION (VDDH = 5V)

7

40

5

30

Vout

= 0.8V

VOUT

= 0.8V

Vout

= 0.65V

VOUT

= 0.65V

4

20

15

2

10

0

0

5

10

15

20

25

30

SAFE OPERATING AREA (SOA) (VDDH = 5V)

40

60

70

80

90

100

TA (°C)

CONDITIONS: 400LFM

CURVE INDICATES TJ = 125°C, IOUT = IMAX, or IVDDH = IVDDH_MAX,

WHICHEVER HAPPENS FIRST

35

30

25

25

IOUT (A)

30

15

Vout=0.8V

VOUT = 0.8V

Vout=1.0V

VOUT = 1.0V

VOUT = 1.2V

Vout=1.2V

10

5

30

40

50

60

70

80

90

100

TA (°C)

CONDITIONS: 200LFM

CURVE INDICATES TJ = 125°C, IOUT = IMAX, or IVDDH = IVDDH_MAX,

WHICHEVER HAPPENS FIRST

www.maximintegrated.com

40

50

40

35

20

30

SAFE OPERATING AREA (SOA) (VDDH = 5V)

toc14

35

0

Vout=0.8V

VOUT = 0.8V

Vout=1.0V

VOUT = 1.0V

VOUT = 1.2V

Vout=1.2V

5

1

IOUT (A)

IOUT (A)

25

3

0

toc13

35

Vout

= 1.8V

VOUT

= 1.8V

Vout

= 1.2V

VOUT

= 1.2V

Vout

= 1V

VOUT

= 1V

IOUT (A)

SYSTEM POWER DISSIPATION (W)

6

SAFE OPERATING AREA (SOA) (VDDH = 5V)

toc12

toc15

20

15

Vout=0.8V

VOUT = 0.8V

Vout=1.0V

VOUT = 1.0V

VOUT = 1.2V

Vout=1.2V

10

5

0

30

40

50

60

70

80

90

100

TA (°C)

CONDITIONS: STILL AIR / NO HEATSINK

CURVE INDICATES TJ = 125°C, IOUT = IMAX, or IVDDH = IVDDH_MAX,

WHICHEVER HAPPENS FIRST

Maxim Integrated │ 9

�MAX20733

Integrated, Step-Down Switching Regulator

PGM3

VCC3

STAT

Pin Configuration

15

14

13

VSENSE+

1

12

VCC2

VSENSE-

2

11

AGND

PGM2

3

10

VCC

PGM1

4

9

OE

VDDH

5

8

BST

7

VX

GND

6

(TOP VIEW)

www.maximintegrated.com

Maxim Integrated │ 10

�MAX20733

Integrated, Step-Down Switching Regulator

Pin Description

PIN

NAME

FUNCTION

1

VSENSE+

Remote-Sense Positive Node. Connect this node to VOUT at the load. A resistive voltage-divider

can be used to regulate the output above the reference voltage.

Remote-Sense Negative Node. Connect this node to ground at the load using a Kelvin connection.

2

VSENSE-

3, 4

PGM2, PGM1

Program Node. Connect this node to ground through a programming resistor and capacitor.

5

VDDH

Power Input Voltage. The high-side MOSFET switch is connected to this node. See the Input

Capacitor section for decoupling requirements.

6

GND

Power Ground Node. The low-side MOSFET switch is connected to this node.

7

VX

Power-Switching Node. Connect this node to the inductor.

8

BST

Bootstrap for High-Side Switch. Connect a 0.22μF ceramic capacitor between BST and VX.

9

OE

Output-Enable Node. This node is used to enable the regulator and has a precise threshold to allow

sequencing of multiple regulators. There is an internal 275kΩ (typ) pulldown on this pin.

10

VCC

Analog/Gate-Drive Supply for the IC from Internal 1.85V (typ) LDO. This node MUST be connected

to three 10µF X5R or better decoupling capacitors with a very short, wide trace. VCC can be

connected to 20kΩ pullups for STAT and OE as shown in Figure 6. Do not connect VCC to other

external loads. Do not overdrive VCC from an external source.

11

AGND

12, 14

VCC2, VCC3

13

STAT

Open-Drain Power-Good/Fault-Status Indication. Connect a pullup resistor to 1.8V or 3.3V.

15

PGM3

Program Node. Connect this node to ground through a programming resistor and capacitor.

www.maximintegrated.com

Analog/Signal Ground. See the PCB Layout section for layout information.

Connect to VCC. Digital factory test input. Must be connected high for normal operation.

Maxim Integrated │ 11

�MAX20733

Integrated, Step-Down Switching Regulator

Block Diagram

VCC

tON

TIMER

STAT

VDDH

LDO

R

S

BST

Q

POWER

SWITCHING

DIGITAL

CONTROL

OE

CURRENT

SENSE

OCP

PGM1

VX

GND

MUX

PGM2

PGM3

VCC

VCC

TELEMETRY

PWM

VSENSE+

ERROR

AMPLIFIER

VCC2

VCC3

VCC

CURRENT

DAC

AGND

VSENSEREFERENCE VOLTAGE AND SOFT START

Operation

Control Architecture

The MAX20733 provides an extremely compact, highefficiency regulator solution with minimal external components and circuit design required. The monolithic solution

includes the top and bottom power switches, gate drives,

precision DAC reference, PWM controller, and fault protections (see the Block Diagram). An external bootstrap

capacitor is used to provide the drive voltage for the top

switch. Other external components include the input and

output filter capacitors, buck inductor, and a few Rs and

Cs to set the operating mode.

technology. Once the PWM modulator forces a low-tohigh transition, the high-side switch is enabled for a fixed

time after which the low-side switch is turned on again. An

error amplifier with an integrator is used to maintain zerodroop operation. The integrator has a transient recovery

time constant of 20µs (typ).

During regulation, the differential voltage between the

VSENSE+ and VSENSE- pins tracks the reference voltage

which can be set to 0.6484V, 0.8984V or 1V via C_SEL1.

The sense pins can be connected to the output voltage

through a voltage-divider so VOUT can be higher than the

reference voltage.

The IC implements an advanced valley current-mode

control algorithm that supports all multilayer ceramic chip

(MLCC) output capacitors and fast transient response. In

steady-state, it operates at a fixed switching frequency.

During loading transients, the switching frequency speeds

up to minimize the output-voltage undershoot. Likewise,

during unloading transients, the switching frequency

slows down to minimize the output-voltage overshoot.

The switching frequency is determined by the high-side

ontime as shown in Equation 1.

The switching frequency can be set to 400kHz, 500kHz,

600kHz, 700kHz, 800kHz, or 900kHz using C_SEL2 and

C_SEL3.

fSW = Switching frequency (MHz)

Voltage regulation is achieved by modulating the low-side

on-time, comparing the difference between the feedback

and reference voltages with the low-side current-sense

signal using Maxim's proprietary integrated current-sense

www.maximintegrated.com

Equation 1:

=

f SW

V

1

× OUT

t H_ON VDDH

where:

tH_ON = On period for high-side switch (μs)

VOUT = Output voltage (V)

VDDH = Input voltage (V)

Maxim Integrated │ 12

�MAX20733

Integrated, Step-Down Switching Regulator

The tH_ON high-side on-time is controlled by the IC to be

proportional to the duty cycle so that the resulting switching

frequency is independent of supply voltage and output voltage.

Equation 2:

t H_ON α

VOUT

VDDH

The tH_ON pulse width is clamped to a minimum of 50ns

(after tSS) and a maximum of 2µs to prevent any unexpected operation during extreme VOUT conditions.

Voltage Regulator Enable and

Turn-On Sequencing

The startup timing is shown in Figure 1. After VDDH is

applied, the IC goes through an initialization time (tINIT)

that takes up to 308μs. After initialization, OE is read.

Once OE is high for more than the 16μs OE filter time

(tOE), BST charging starts and is performed for 8μs

(tBST), and then the soft-start ramp begins. The soft-start

ramp time (tSS) is 3ms or 1.5ms, depending on the user’s

programmed value. VOUT ramps up linearly during the

soft-start ramp time. If there are no faults, the STAT pin is

released from being held low after the completion of the

soft-start ramp time plus the user-programmable STAT

blanking time (tSTAT) of 125μs or 2ms. If OE is pulled low,

the IC shuts down.

Soft-Start Control

The initial output-voltage behavior is determined by a

linear ramp of the internal reference voltage from zero

to the final value (tSS in Figure 1). The ramp time tSS is

programmable from to 1.5ms or 3ms.

If the regulator is enabled when the output voltage has

a residual voltage, the system will not regulate until the

reference voltage ramps above this residual value. In this

case, the tOE (OE valid to onset of regulation) specification is extended by the time required for the desired voltage startup ramp to reach the actual residual output voltage, but the time to reach the steady-state output voltage

is unchanged.

If the residual voltage is higher than the set output voltage, neither the high-side nor the low-side switch turns

on by the end of tSS. Under these conditions, switching

begins after tSS.

The IC exhibits a nonlinearity during startup. This behavior is normal and does not have an adverse effect

on system operation. With the circuit of Figure 6, the

typical nonlinearity is < 50mV with RGAIN = 0.9mV/A,

160mV with RGAIN = 1.8mV/A, and 320mV with RGAIN =

3.6mV/A. The nonlinearity gets proportionately smaller as

COUT increases.

Remote Output-Voltage Sensing

To ensure the most accurate sensing of the output voltage, a differential voltage-sense topology is used, with a

negative remote-sense pin provided. Point-of-load sensing compensates for voltage drops between the output

of the regulator and its load and provides the highest

regulation accuracy. The voltage-sensing circuit features

excellent common-mode rejection to further improve loadvoltage regulation.

tINIT

VCC

tOE

SHUTDOWN

OE or OPERATE

tBST

VOUT

tSS

STAT

tSTAT

tINIT : Initialization, 308µs.

tOE : OE enable filter time, 16µs. If OE enabled earlier than tINIT completion, it is ignored until tINIT completes.

tBST : BST charging time, 8µs.

tSS : Soft-start time per user selection, 0.75ms to 6ms.

tSTAT : STAT blanking time, 2ms or 125µs through user selection.

Figure 1. Startup Timing

www.maximintegrated.com

Maxim Integrated │ 13

�MAX20733

Integrated, Step-Down Switching Regulator

Protection and Status Operation

Output-Voltage Protection

The feedback voltage is continuously monitored for both

undervoltage and overvoltage conditions. The typical

fault-detection threshold is 13% above and 9% below the

reference voltage (see Electrical Characteristics table). If

the output voltage falls below the power-good protection

(PWRGD) threshold beyond the filter time, the regulator

status (STAT) output goes low but the system continues

to operate, attempting to maintain regulation.

If the output voltage rises above the overvoltage-protection (OVP) threshold beyond the filter time, the STAT pin

is lower and the system shuts down until the output voltage falls within the valid range.

Current Limiting and Short-Circuit Protection

The regulator’s valley current-mode control architecture

provides inherent current limiting and short-circuit protection. The bottom switch’s instantaneous current is monitored using integrated current sensing and controlled on a

cycle-by-cycle basis within the control block.

Current clamping occurs when the minimum instantaneous (“valley”) low-side switch-current level exceeds the

OCP threshold current, as shown in Figure 2. In this situation, turn-on of the high-side switch is prevented until the

current falls below the threshold level. Since the inductor valley current is the controlled parameter, the average current delivered during positive current clamping

remains a function of several system-level parameters.

Note that IOCP has hysteresis and the value drops down

to IOCP2 once it has been triggered as shown in Figure 2.

Undervoltage Lockout (UVLO)

The regulator internally monitors VDDH with an undervoltage-lockout (UVLO) circuit. When the input supply voltage

is below the UVLO threshold, the regulator stops switching, and the STAT pin is driven low. For UVLO levels, refer

to the Electrical Characteristics table.

Overtemperature Protection (OTP)

The overtemperature-protection level can be set to 150°C

or 130°C through R_SEL2. If the die temperature reaches

the OTP level during operation, the regulator is disabled

and the STAT pin is driven low. Overtemperature is a nonlatching fault, with the hysteresis shown in the Electrical

Characteristics table.

Regulator Status

The regulator status (STAT) signal provides an open-drain

output, consistent with CMOS logic levels, that indicates

whether the regulator is functioning properly. An external

pullup resistor is required for connecting STAT to VCC or

another 1.8V or 3.3V supply.

Table 1. Summary of Fault Actions

FAULT

ACTION

Power Good

(Output Undervoltage)

STAT LOW

Output OVP

STAT LOW, Shutdown and Restart

Overtemperature

STAT LOW, Shutdown and Restart

Supply Fault (VDDH_UVLO;

STAT LOW, Shutdown and Restart

VCC_UVLO)

BST Fault

STAT LOW, Shutdown and Restart

IOCP(AVG)

IOCP

IOCP2

IOCP(AVG) = IOCP2 +

I

L

1

2

( VDDH − VOUT ) x

tH_ON

LOUT

where:

IOCP2 = IOCP - Hysteresis

Figure 2. Inductor Current During Current Limiting

www.maximintegrated.com

Maxim Integrated │ 14

�MAX20733

Integrated, Step-Down Switching Regulator

The STAT pin is low while the regulator is disabled. The

STAT pin goes high after the startup ramp is completed

plus the programmed tSTAT blanking interval, if the output

voltage is within the PWRGD/OVP regulation window.

The STAT pin is an open-drain output and is 3.3V tolerant.

The pin will remain low when VDDH is not present.

PGM1, 2 and 3 Pin Functionality

The STAT pin is driven low when one or more of the following conditions exists:

The parasitic loading on the PGM1:PGM3 pins must be

limited to less than 20pF and greater than 20MΩ to avoid

interfering with the R_SEL and C_SEL decoding.

●●

A PWRGD fault (see the Output-Voltage Protection

section).

●●

The VSENSE- pin is left unconnected or shorted to

VDDH.

●●

The die temperature has exceeded the temperatureshutdown threshold shown in the Electrical Characteristics

table.

●●

The OVP circuit has detected that the output voltage

is above the tolerance limit.

●●

The supply voltage has dropped below the UVLO

threshold.

●●

A fault is detected on the BST node such as shorted

or open bootstrap capacitor.

The ensuing startup follows the same timing as shown in

Figure 1.

Table 2. PGM1 Pin R_SEL1 Values

R(kΩ) ±1%

SOFT-START TIME (ms)

1.78

3

46.4

1.5

Table 3. PGM1 Pin C_SEL1 Values

C (pF) ±20%

VREF (V)

Open

0.6484

220

0.8984

1000

1

Table 4. PGM2 Pin R_SEL2 Values

R(kΩ) ±1%

OTP (°C)

tSTAT (µs)

1.78

150

2000

2.67

150

125

4.02

130

2000

6.04

130

125

www.maximintegrated.com

The PGM1:PGM3 pins are used to set up some of the

key programmable features of the regulator IC. A resistor

and capacitor are connected to the PGM_ pins and their

values are read during power-up initialization (e.g., power

must be cycled to re-read the values).

Table 5. PGM2 Pin C_SEL2 Values

C(pF) ±20%

fSW FREQUENCY BAND

Open

Even

220

Odd

Table 6. PGM3 Pin C_SEL3 Values

C(pF) ±20%

EVEN BAND fSW

FREQUENCY (kHz)

ODD BAND fSW

FREQUENCY (kHz)

Open

400

500

220

600

700

1000

800

900

Table 7. PGM3 Pin R_SEL3 Values

R (kΩ) ±1%

RGAIN (mΩ)

OCP *

1.78

3.6

Setting 0

2.67

3.6

Setting 1

4.02

3.6

Setting 2

6.04

3.6

Setting 3

9.09

1.8

Setting 0

13.3

1.8

Setting 1

20

1.8

Setting 2

30.9

1.8

Setting 3

46.4

0.9

Setting 0

71.5

0.9

Setting 1

107

0.9

Setting 2

162

0.9

Setting 3

* See Electrical Characteristics table for values

Maxim Integrated │ 15

�MAX20733

Integrated, Step-Down Switching Regulator

Reference Design

The typical application schematic is shown in Figure 3 and Table 8 shows optimum component values for common output

voltages.

VDDH

CVCC

1.8V or 3.3V

1.8V or 3.3V

COMPLIANT I/O

RSTAT

STAT

OE

U1

VCC

VCC2

VCC3

CIN

VDDH

CBST

BST

STAT

OE

LOUT

VOUT

VX

MAX20733

C_SEL1

PGM1

PGM2

PGM3

R_SEL1

RFB2

R_SEL2

C_SEL3

R_SEL3

COUT

GND

AGND

C_SEL2

RFB1

VSENSE+

VSENSE-

Figure 3. Typical Application Circuit

Table 8. Reference Design Component Values

VOUT RFB1 RFB2 R_SEL1 C_SEL1 R_SEL2

(V)

(kΩ) (kΩ)

(kΩ)

(pF)

(kΩ)

C_SEL2 R_SEL3 C_SEL3 RGAIN

(pF)

(kΩ)

(pF)

(mΩ)

VREF

(V)

fSW

(kHz)

LOUT

(nH)

COUT

0.6484

1

Open

1.78

Open

2.67

Open

162

Open

0.9

0.6484

400

170

6 x 100μF + 2

x 470μF

0.8

1.37

5.9

1.78

Open

2.67

Open

162

Open

0.9

0.6484

400

170

6 x 100μF + 2

x 470μF

1

1.87

3.48

1.78

Open

2.67

Open

162

Open

0.9

0.6484

400

170

6 x 100μF + 2

x 470μF

1.2

1.74

2.05

1.78

Open

2.67

Open

162

Open

0.9

0.6484

400

170

6 x 100μF + 2

x 470μF

1.8

3.09

1.74

1.78

Open

2.67

Open

162

220

0.9

0.6484

600

170

6 x 100μF + 2

x 470μF

3.3

5.62

1.37

1.78

Open

2.67

Open

107

220

0.9

0.6484

600

210

6 x 100μF + 2

x 470μF

5.0

7.15

1.07

1.78

Open

2.67

Open

107

220

0.9

0.6484

600

210

6 x 100μF + 2

x 470μF

Note: For input caps, see the Input Capacitor Selection section.

www.maximintegrated.com

Maxim Integrated │ 16

�MAX20733

Integrated, Step-Down Switching Regulator

Average Input Current Limit

The input current of VDDH is given by Equation 3. VOUT,

IOUT, and VDDH should be properly chosen so that the

average input current does not exceed 6A (IVDDH_MAX).

Equation 3:

I VDDH =

VOUT × I OUT

VDDH × η

where:

VOUT = Output voltage

IOUT = Output current

VDDH = Input voltage

η = Efficiency (refer to the Typical Operating

Characteristics section)

Output-Voltage Setting

If an output voltage not listed in Table 8 is required, calculate new values for RFB1 and RFB2 (as discussed below)

and use the other circuit values of the closest output voltage in Table 8, or calculate them as shown below.

The output voltage is set by the VREF DAC and divider

ratio of resistors RFB1 and RFB1 per Equation 4. The

IC regulates the VSENSE+ pin to the reference voltage

(VREF), which is set by the DAC. Upon power-up, the DAC

voltage initializes to one of the user-selectable VREF voltages. The divider resistors are chosen to give the correct

output voltage and to have an approximate parallel resistance of RPAR = 1kΩ for best common-mode rejection

of the error amplifier. In applications requiring less than

10mV peak-to-peak output-voltage ripple, setting a lower

DAC reference voltage such as 0.6484V is recommended

because the part will have less DAC voltage noise.

where:

RFB1 = Top divider resistor

RFB2 = Bottom divider resistor

RPAR = Desired parallel resistance of RFB1 and RFB2

VOUT = Output voltage

VREF = 0.6484V, 0.8984V, or 1.0V (set by C_SEL1)

Control-Loop Stability

The IC uses valley current-mode control that is stabilized

by selecting appropriate values of COUT and RGAIN. No

compensation network is required. For stability, the loop

bandwidth (BW) should be 100kHz or less. Consider the

case of using MLCC output capacitors that have nearly

ideal impedance characteristics in the frequency range of

interest with negligible ESR and ESL. The loop bandwidth

can be approximated by breaking the loop into gain terms

as outlined below.

1) The IC’s valley current-mode control scheme has an

effective transconductance gain of 1/RGAIN.

2) For MLCC capacitors, the output capacitors contribute an impedance gain of 1/(2 x π x COUT x f).

3) The feedback-divider contributes an attenuation of

KDIV = RFB2/(RFB1 + RFB2).

4) An inherent high-frequency pole located at 150kHz.

When the BW is 100kHz or less, the high-frequency pole

can be ignored and the approximate loop gain and BW

are given by Equation 6.

Equation 6:

LOOP_GAIN (f) =

Equation 4:

BW =

R

VOUT

= VREF × 1 + FB1

R FB2

OR

BW =

where:

VREF = 0.6484V, 0.8984V, or 1.0V (set by C_SEL1).

The divider resistors are then given by Equation 5.

Equation 5:

R PAR

R

=

FB1 VOUT ×

VREF

R PAR

R=

FB2 R FB1 ×

−

R

R

PAR

FB1

www.maximintegrated.com

K DIV

2 × π × R GAIN × C OUT × f

K DIV

2 × π × R GAIN × C OUT

1

2 × π × R GAIN_EFF × C OUT

where:

RGAIN_EFF = RGAIN/KDIV

For stability, RGAIN and COUT should be chosen so that

BW < 100kHz.

The available RGAIN settings are shown in Table 7. When

choosing which RGAIN setting to use, one should consider

that while higher RGAIN allows the loop to be stabilized with

less COUT, less COUT generally results in higher ripple and

larger transient overshoot and undershoot, so there needs

to be a balance.

Maxim Integrated │ 17

�MAX20733

Integrated, Step-Down Switching Regulator

Integrator

The IC has an integrator included in its error amplifier that

was ignored in the above equations for simplicity. The

integrator only adds gain at low frequencies, so it does

not really effect the loop BW calculation. The purpose of

the integrator is to improve load regulation. The integrator

adds a factor of (1/tREC + s)/s to the loop gain.

net ESR of the COUT bank is not negligible compared

to RGAIN/KDIV, the inductor current ripple is effectively

sensed by the ESR and adds to the RGAIN_EFF as shown

in Equation 8.

Equation 8:

R GAIN_EFF

=

Step Response

RGAIN_EFF is important since it determines the smallsignal transient response of the regulator. When a

load step is applied that does not exceed the slew-rate

capability of the inductor current, the regulator responds

linearly and VOUT temporarily changes by the amount of

VOUT_ERROR (see Equation 7).

Equation 7:

VOUT_ERROR

=

I STEP × R GAIN_EFF

The capacitor’s ESR also introduces a zero into the loop

gain. The inherent high-frequency pole helps to compensate this zero. For a more in-depth view of the effect of

circuit values on regulator performance, the Maxim

Simplis model and evaluation kit can be used. It is recommended to simulate and/or test regulator performance

when using values other than the recommended component values.

The integrator causes VOUT to recover to the nominal

value with a time constant of tREC = 20μs. The regulator

can be modeled to a first-order by the averaged smallsignal equivalent circuit shown in Figure 4. Here, VEQ is

an ideal voltage source, REQ is an equivalent lossless

resistance created by the control-loop action, and LEQ is

an equivalent inductance. Note that LEQ is not the same

as the actual LOUT inductor which has been absorbed

into the model. COUT is the actual output capacitance.

tREC RGAIN_EFF

LEQ

RGAIN_EFF

VOUT

REQ

COUT

Output-Capacitor ESR

In the above control-loop discussion, the case of MLCC

output capacitors has been considered. Another case

worth mentioning is the use of output capacitors with

more significant ESR. This may be considered as long

as the capacitors are rated to handle the inductor current ripple and expected surge currents. Thus far, it has

been assumed that COUT is comprised of MLCCs and

the net ESR is negligible compared to RGAIN/KDIV. If the

R GAIN

+ ESR

K DIV

VOUT

VEQ

GND

Figure 4. Averaged Small-Signal Equivalent Circuit of Regulator

Note: The large-signal transient response is approximately

the larger between the VOUT_ERROR and the Unloading

Transient.

Table 9. Recommended Inductors

COMPANY

VALUE

(nH)

ISAT

(A)

RDC

(mΩ)

FOOTPRINT

(mm)

HEIGHT

(mm)

PART

NUMBER

WEBSITE

Cooper

170

60

0.29

10.4 x 8.0

7.5

FP1007R3-R17-R

www.cooperindustries.com

Pulse

210

64

0.32

13.5 x 13.0

8.0

PA0513.211NLT

www.pulseelectronics.com

Pulse

260

55

0.32

13.5 x 13.0

8.0

PA0513.261NLT

www.pulseelectronics.com

Pulse

320

45

0.32

13.5 x 13.0

8.0

PA0513.321NLT

www.pulseelectronics.com

Pulse

440

30

0.32

13.5 x 13.0

8.0

PA0513.441NLT

www.pulseelectronics.com

www.maximintegrated.com

Maxim Integrated │ 18

�MAX20733

Integrated, Step-Down Switching Regulator

Table 10. MLCC Input Capacitors

CASE SIZE

VALUE

(µF)

TEMPERATURE

RATING

VOLTAGE

RATING

T

(NOTE 1)

COMPANY

0603

1

X7S

X7R

16V

0.8

(Note 2)

Murata

TDK

GRM188C71C105KA12D

C1608X7R1C105K

0805

2.2

X7R

25V

16V

16V

1.25

1.25

1.25

Murata

TDK AVX

GRM21BR71E225KA73L

C2012X7R1C225M

0805YC225MAT

0805

4.7

X7R

16V

1.25

Murata

GRM21BR71C475K

1206

4.7

X7R

16V

1.65

AVX

Murata

1206YC475MAT

GRM31CR71C475KA01L

1206

10

X7R

16V

1.65

Murata

TDK AVX

GRM31CR71C106KAC7L

C3216X7R1C106M

1206YC106MAT

1210

10

X7R

16V

25V

2.0

2.5

Murata

TDK

GRM32DR71C106KA01L

C3225X7R1E106M

1210

22

X7R

16V

2.45

2.5

2.5

AVX

Murata

TDK

1210YC226MAT

GRM32ER71A476K

C3225X7R1C226M

PART NUMBER

Note 1: T indicates nominal thickness in mm.

Note 2: Indicates capacitors with nominal thickness smaller than the minimum FCQFN package thickness.

Table 11. Recommended Output Capacitors

COMPANY

VALUE

(µF)

TEMP.

RATING

VOLT.

RATING

CASE

SIZE

T

(NOTE)

AVX

22

22

08054D226MAT2A

12066D226MAT2A

X5R

X5R

4V

6.3V

0805

1206

1.3

1.65

www.avxcorp.com

Murata

22

22

22

GRM21BR60J226ME39L

GRM31CR60J226KE19L

GRM32DR60J226KA01L

X5R

X5R

X5R

6.3V

6.3V

6.3V

0805

1206

1210

1.25

1.6

2.0

www.murata.co.jp

Panasonic

22

22

22

ECJ3YB0J226M

ECJHVB0J226M

ECJ3Y70J226M

X5R

X5R

X7R

6.3V

6.3V

6.3V

1206

1206

1206

1.6

0.85

1.65

www.panasonic.com

Taiyo Yuden

22

22

22

AMK212BJ226MG

JMK316BJ226ML

JMK325BJ226MY

X5R

X5R

X5R

4V

6.3V

6.3V

0805

1206

1210

1.25

1.6

1.9

www.taiyo-yuden.com

TDK

22

22

22

22

C2012X5R0J226M

C3216X5R0J226M

C3225X5R0J226M

C3216X6S0J226M

X5R

X5R

X5R

X6S

6.3V

6.3V

6.3V

6.3V

0805

1206

1210

1206

1.25

1.6

1.6

1.6

www.component.tdk.com

PART NUMBER

WEBSITE

Note: T indicates nominal thickness in mm.

www.maximintegrated.com

Maxim Integrated │ 19

�MAX20733

Integrated, Step-Down Switching Regulator

The performance data shown in the Typical Operating

Characteristics section was taken using the Maxim EV kit

and component values in Table 8. For most applications,

these are the optimum values to use. Table 9 through

Table 11 show suitable part numbers for input and output

capacitors and the inductor.

Inductor Selection

The output inductor has an important influence on the

overall size, cost, and efficiency of the voltage regulator.

Since the inductor is typically one of the larger components in the system, a minimum inductor value is particularly important in space-constrained applications. Smaller

inductor values also permit faster transient response,

reducing the amount of output capacitors needed to maintain transient tolerances.

LOUT = Output inductance

VDDH = Input voltage

VOUT = Output voltage

From Equation 10, for the same switching frequency,

ripple current increases as L decreases. This increased

ripple current results in increased AC losses, larger peak

current, and for the same output capacitance, results in

increased output-voltage ripple.

IOUTRIPPLE should be set to 25% to 50% of the IC’s

rated output current. A suitable inductor value can then

be found by solving Equation 10 for inductance as in

Equation 11 and Equation 12.

Equation 11:

For any buck regulator, the maximum current slew rate

through the output inductor is given by Equation 9.

Equation 9:

SlewRate

=

dIL

VL

=

dt L OUT

L OUT =

And assuming IOUTRIPPLE = 0.25 x IOUT for a typical

inductor value, see Equation 12.

Equation 12:

where:

OUT

IL = Inductor current

LOUT = Output inductance

VL = VDDH - VOUT during high-side FET conduction and

-VOUT during low-side FET conduction

Equation 9 shows that larger inductor values limit the

regulator’s ability to slew current through the output inductor in response to step-load transients. Consequently,

more output capacitors are required to supply (or store)

sufficient charge to maintain regulation while the inductor

current ramps up to supply the load.

In contrast, smaller inductor values increase the regulator’s maximum achievable slew rate and decrease

the necessary capacitance, at the expense of higher

ripple current. The peak-to-peak ripple current is given by

Equation 10.

I OUTRIPPLE =

L OUT

where:

tH_ON = High-side switch on-time (based on nominal

VOUT) (see Equation 1)

www.maximintegrated.com

VOUT (VDDH

VOUT )

VDDH × (0.25 × I OUT ) × f SW

So, for a 35A regulator running at 400kHz with VDDH =

12V and VOUT = 1V, Equation 13 shows the target value

for the inductor.

Equation 13:

L OUT =

1× (12 − 1)

12 × 0.25 × 35 × 400,000

= 262nH

The saturation current rating of the inductor is another

important consideration. At current limit, the peak inductor

current is given Equation 14.

Equation 14:

Equation 10:

t H_ON × (VDDH − VOUT )

VOUT (VDDH − VOUT )

VDDH × I OUTRIPPLE × f SW

IPK = I OCP + I OUTRIPPLE

where:

IOCP = Overcurrent-protection trip point (see Electrical

Characteristics and Current Limiting and Short-Circuit

Protection sections)

IOUTRIPPLE = Peak-to-peak inductor current ripple,

defined above

Maxim Integrated │ 20

�MAX20733

Integrated, Step-Down Switching Regulator

For proper OCP operation of the regulator, it is important

that IPK never exceeds the saturation current rating of

the inductor (ISAT). It is recommended that a margin of at

least 20% is included between IPK and ISAT as shown in

Equation 15.

Equation 15:

I SAT > 1.2 × IPK

Also, note that during a hard VOUT short circuit,

IOUTRIPPLE increases because VOUT went to zero in

Equation 10.

Finally, the power dissipation of the inductor influences

the regulation efficiency. Losses in the inductor include

core loss, DC resistance loss and AC resistance loss.

For the best efficiency, use inductors with core material

exhibiting low loss in the range of 0.5MHz to 2MHz and

low-winding resistance.

Table 9 provides a summary of recommended inductor

suppliers and part numbers.

Output Capacitor Selection

Output voltage ripple is another important consideration

in the selection of output capacitors. For a buck regulator operating in CCM, the total voltage ripple across the

output capacitor bank can be approximated as the sum of

three voltage waveforms: 1) the triangle wave that results

from multiplying the AC ripple current by the ESR, 2) the

square wave that results from multiplying the ripple current slew rate by the ESL and 3) the piece wise quadratic

waveform that results from charging and discharging the

output capacitor. Although the phasing of these three

components does impact the total output ripple, a common approximation is to ignore the phasing and to find

the upper bound of the peak-to-peak ripple by summing

all three components, as shown in Equation 17.

Equation 17:

VDDH I OUTRIPPLE

V=

+

PP ESR(I OUTRIPPLE ) + ESL

L OUT 8 × f SW × C OUT

where:

ESR = Equivalent series resistance at the output

The minimum recommended output capacitance for stability is given in the Control-Loop Stability section and is

normally implemented using several 100µF 1206 (or similar) MLCCs. For low slew rate transient loads, RGAIN_EFF

determines the VOUT_ERROR for a given load step per

the small-signal model as discussed above. In this case,

COUT has no effect on the VOUT_ERROR.

IOUTRIPPLE = Peak-to-peak inductor current ripple

However, in the event that the slew rate of the load transient greatly exceeds the slew rate of the inductor current,

the transient VOUT error may be larger than predicted by

the small-signal model. In this case, the VOUT loading

and unloading transients can be approximated by taking

the larger result between Equation 7 and Equation 16.

COUT = Output capacitance

Equation 16:

I

LOUT × ISTEP + OUTRIPPLE

2

LOADINGTRANSIENT(V) =

2 × COUT × ( VDDH − VOUT )

2

2

I

LOUT × ISTEP + OUTRIPPLE

tH _ ON

2

+I

UNLOADINGTRANSIENT(V)

=

STEP ×

2 × COUT × VOUT

COUT

In order to meet an aggressive transient specification,

COUT may have to be increased and/or LOUT may

have to be decreased. However, note that decreasing

LOUT results in larger inductor ripple current and thus

decreased efficiency and increased output ripple.

www.maximintegrated.com

ESL = High-frequency equivalent series inductance at

output

VDDH = Input voltage

LOUT = Output inductance

fSW = Switching frequency

In a typical MAX20733 application with a bank of 0805,

X5R, 6.3V, and 22µF output capacitors, these three components are roughly equal.

The ESL effect of an output capacitor on output-voltage

ripple cannot be easily estimated from the resonant frequency; the high-frequency (10MHz or above) impedance

of that capacitor should be used. PCB traces and vias in the

VOUT/GND loop contribute additional parasitic inductance.

The final considerations in the selection of output capacitors are ripple-current rating and power dissipation. Using

a conservative design approach, the output capacitors

should be designed to handle the maximum peak-to-peak

AC ripple current experienced in the worst-case scenario. Because the recommended output capacitors have

extremely low-ESR values, they are typically rated well

above the current and power stresses seen here. For the

triangular AC ripple current at the output, the total RMS current and power is given by Equation 18 and Equation 19.

Maxim Integrated │ 21

�MAX20733

Integrated, Step-Down Switching Regulator

Equation 18:

current that the input capacitor must withstand can be

approximated using Equation 21.

I

IRMS_COUT = OUTRIPPLE

12

Equation 21:

where:

IOUTRIPPLE = Peak-to peak ripple current value.

Equation 19:

=

PCOUT IRMS_COUT 2 × ESR

where ESR is the equivalent series resistance of the

entire output capacitor bank

IRMS_CIN =

It is recommended to choose the main MLCC input

capacitance to control the peak-to-peak input-voltage

ripple to 2% to 3% of its DC value in accordance with

Equation 20.

Equation 20:

I

× VOUT × (VDDH − VOUT )

C IN = MAX

f SW × VDDH 2 × VINPP

(

With an equivalent series resistance of the bulk input

capacitor bank (ESRCIN), the total power dissipation in

the input capacitors is given by Equation 22.

Equation 22:

=

PCIN IRMS_CIN 2 × ESR CIN

Resistor Selection and its Effect

on DC Output Voltage Accuracy

RFB1 and RFB2 set the output voltage as described in

Equation 4. The tolerance of these resistors affects the

accuracy of the set output voltage. Due to the form of

Equation 4, the effect is higher at higher output voltages.

Figure 5 shows the effect of 0.1% tolerance resistors over

a range of output voltages. For different tolerance resistors, multiply the output-voltage error by the resistors’ tolerances divided by 0.1%. For example, for 0.5% tolerance

resistors, multiply the output error shown by 5. To obtain

accuracy overtemperature, for a worst case, the temperature coefficients multiplied by the temperature range

should be added to the tolerance (i.e., for 25ppm/°C

resistors over a 50°C excursion, add 0.125% to the 25°C

tolerance).The error due to the voltage feedback resistors’ tolerance, RFB1 and RFB2 should be added to the

output-voltage tolerance due to the IC’s feedback-voltage

accuracy shown in the Electrical Characteristics table.

)

0.180%

0.160%

where:

0.140%

CIN = Input capacitance (MLCC)

VDDH = DC input voltage

VOUT = DC output voltage

fSW = Switching frequency (CCM)

VINPP = Target peak-to-peak input-voltage ripple

Because the bulk input capacitors must source the pulsed

DC input current of the regulator, the power dissipation

and ripple current rating for these capacitors are far more

important than that for the output capacitors. The RMS

www.maximintegrated.com

0.120%

ERROR (%)

IMAX = Maximum load current

VDDH

where ILOAD is the output DC load current.

Input Capacitor Selection

The selection and placement of input capacitors are

important considerations. High-frequency input capacitors

serve to control switching noise. Bulk input capacitors

are designed to filter the pulsed DC current drawn by

the regulator. For the best performance, lowest cost and

smallest size of the MAX20733 systems, MLCC capacitors with 1210 or smaller case sizes, capacitance values

of 47µF or smaller, 16V or 25V voltage ratings and X5R or

better temperature characteristics are recommended as

bulk. The minimum recommended value of capacitance

are 2 x 47µF (bulk) and 1.0µF + 0.1µF (high frequency).

Smaller values of bulk capacitance can be used in direct

proportion to the maximum load current.

ILOAD VOUT (VDDH − VOUT )

0.100%

εVOUT = 2εR(VOUT - VREF)/VOUT

0.080%

0.060%

0.040%

0.020%

0.000%

1

1.5

2

2.5

3

3.5

4

4.5

5

VOUT/VREF RATIO

Figure 5. DC Accuracy Impact Showing Effect of 0.1%

Tolerance for RFB1 and RFB2

Maxim Integrated │ 22

�MAX20733

Integrated, Step-Down Switching Regulator

PCB Layout

PCB layout can dramatically affect the performance of the

regulator. A poorly designed board can degrade efficiency,

noise performance, and even control-loop stability. At

higher switching frequencies, layout issues are especially

critical.

As a general guideline, the input capacitors and the

output inductor should be placed in close proximity to

the regulator IC, while the output capacitors should be

lumped together as close as possible to the load. Traces

to these components should be kept as short and wide

as possible in order to minimize parasitic inductance and

resistance. Traces connecting the input capacitors and

VDDH (power input node) on the IC require particular

attention since they carry currents with the largest RMS

values and fastest slew rates. According to best practice,

the input capacitors should be placed as close as possible to the input supply pins with the smallest package

high-frequency capacitor being the closest to the IC and

no more than 60 mils from the IC pins. Preferably, there

should be an uninterrupted ground plane located immediately underneath these high-frequency current paths, with

the ground plane located no more than 8 mils below the

top layer. By keeping the flow of this high-frequency AC

current localized to a tight loop at the regulator, electromagnetic interference (EMI) can be minimized.

Voltage-sense lines should be routed differentially directly

from the load points. The ground plane can be used as a

shield for these or other sensitive signals to protect them

from capacitive or magnetic coupling of high-frequency

noise.

www.maximintegrated.com

For remote-sense applications where the load and regulator IC are separated by a significant distance or impedance, it is important to place the majority of the output

capacitors directly at the load. Ideally, for system stability,

all the output capacitors should be placed as close as

possible to the load. In remote-sense applications, common-mode filtering is necessary to filter high-frequency

noise in the sense lines.

The following layout recommendations should be used for

optimal performance:

●●

It is essential to have a low-impedance and uninterrupted ground plane under the IC and extended out

underneath the inductor and output capacitor bank.

●●

Multiple vias are recommended for all paths that

carry high currents (i.e., GND, VDDH, VX). Vias

should be placed close to the chip to create the

shortest possible current loops. Via placement must

not obstruct the flow of currents or mirror currents in

the ground plane.

●●

A single via in close proximity to the chip should

be used to connect the top layer AGND trace to the

second layer ground plane, it must not be connected

to the top power ground area.

●●

The feedback-divider and compensation network

should be close to the IC to minimize the noise on

the IC side of the divider.

Gerber files with layout information and complete reference designs can be obtained by contacting a Maxim

account representative.

Maxim Integrated │ 23

�Soft Start = 3ms

Vref = 0.6484V

Fsw = 400kHz

Rgain = 0.9 milliohms

OTP = 150C

TSTAT = 125us

OCP = Setting 3

Freq Band = Even

R2

162K

0402

PGM3

PGM1

R1

1.78K

0402

PGM2

R12

2.67K

0402

OE

C32

1000pF

0402

C54

DNS

0402

20K

STAT

20K

R8 0402

C23

DNS

0402

C4

DNS

0402

C51

10uF

X5R

0603

PGM3

PGM2

PGM1

VCC3

VCC2

OE

STAT

C36

10uF

X5R

0603

VX

BST

U1

VSENSE-

VSENSE+

MAX20733

DNS = Do Not Stuff

AGND

R5 0402

C9

10uF

X5R

0603

VCC

VCC

VDDH

VDDH

www.maximintegrated.com

GND

C3

0.1uF

X7R

0402

SENSE-

SENSE+

VX

BST

C8

0.22uF

X7R

0402

C7

1uF

X7R

0603

Diff Pair

C5

47uF

X5R

1206

170nH

L1

C6

47uF

X5R

1206

C10

47uF

X5R

1206

VDDH

R9

3.48K

0402

R6

1.87K

0402

SENSE_VOUT

C11

47uF

X5R

1206

Diff Pair

INPUT SUPPLY

0 0402

R11

0

R4 0402

C24

0.01uF

0402

C12-17

6x100uf

1206

+

C28-29

2x470uF

5 m-ohms

VOUT = 1V

VOUT

MAX20733

Integrated, Step-Down Switching Regulator

Figure 6. Reference Schematic (VDDH = 4.5V to 16V, VOUT = 1V)

Maxim Integrated │ 24

�MAX20733

Integrated, Step-Down Switching Regulator

Ordering Information

TEMP RANGE

PIN-PACKAGE

MAX20733EPL+

PART

-40°C to +125°C

15 FCQFN

MAX20733EPL+T

-40°C to +125°C

15 FCQFN

+Denotes a lead(Pb)-free/RoHS-compliant package.

T = Tape and reel.

www.maximintegrated.com

Maxim Integrated │ 25

�MAX20733

Integrated, Step-Down Switching Regulator

Revision History

REVISION

NUMBER

REVISION

DATE

0

10/16

DESCRIPTION

Initial release

PAGES

CHANGED

—

For pricing, delivery, and ordering information, please contact Maxim Direct at 1-888-629-4642, or visit Maxim Integrated’s website at www.maximintegrated.com.

Maxim Integrated cannot assume responsibility for use of any circuitry other than circuitry entirely embodied in a Maxim Integrated product. No circuit patent licenses

are implied. Maxim Integrated reserves the right to change the circuitry and specifications without notice at any time. The parametric values (min and max limits)

shown in the Electrical Characteristics table are guaranteed. Other parametric values quoted in this data sheet are provided for guidance.

Maxim Integrated and the Maxim Integrated logo are trademarks of Maxim Integrated Products, Inc.

© 2016 Maxim Integrated Products, Inc. │ 26

�