�������

�� �

����

����

�����

��� ����������� ���������

���� �������

��������� ����� � ���������

SLOS127 − JUNE 1993

D Single-Supply Operation With Rail-to-Rail

D

D

D

D

D

D

D

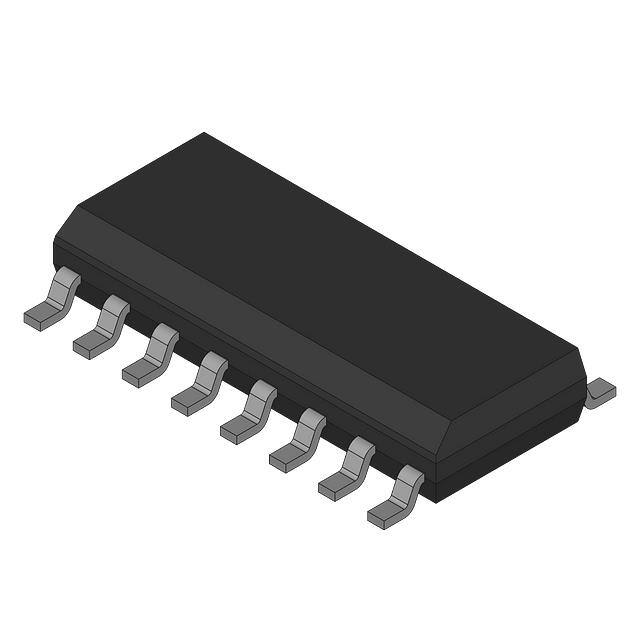

DW PACKAGE

(TOP VIEW)

Inputs

± 30-mA Min Short-Circuit Output Current

Wide VCC Range . . . 3.5 V to 15 V

VOUT Supplies up to 100 mA for External

Loads

Shutdown Mode

External 2.5-V Voltage Reference Available

40-V/µs Slew Rate Typ

High Gain-Bandwidth Product . . . 10 MHz

1 OUT

1 IN −

1 IN +

VCC −

VOUT

VREF

OSC

VIN

1

16

2

15

3

14

4

13

5

12

6

11

7

10

8

9

VCC +

2 OUT

2 IN −

2 IN +

CAP −

GND

CAP +

FB/SD

description

The TLE2682 offers the advantages of JFET-input operational amplifiers and rail-to-rail common-mode input

voltage range with the convenience of single-supply operation. By combining a switched-capacitor voltage

converter with a dual operational amplifier in a single package, Texas Instruments now gives circuit designers

new options for conditioning low-level signals in single-supply systems.

The TLE2682 features two high-speed, high-output drive JFET-input operational amplifiers with a switchedcapacitor building block. Using two external capacitors, the switched-capacitor network can be configured as

a voltage inverter generating a negative supply voltage capable of sourcing up to 100 mA. This supply functions

not only as the amplifier’s negative rail but is also available to drive external circuitry. In this configuration, the

amplifier common-mode input voltage range extends from the positive rail to below ground, thus providing true

rail-to-rail inputs from a single supply. Furthermore, the outputs can swing to and below ground while sinking

over 25 mA. This feature was previously unavailable in operational amplifier circuits. The TLE2682 operational

amplifier section has output stages that can drive 20-mA loads to 2.3 V with a 5-V rail. With a 2-mA load, the

output swing extends to 3.9 V.

This amplifier design features a 25-V/µs minimum slew rate, which results in a high-power bandwidth. Settling

time to 0.1% of a 10-V step (1-kΩ/100-pF load) is approximately 400 ns. Gain-bandwidth product is typically

10 MHz with an 8-MHz minimum. The TLE2682 offers significant speed and noise advantages at a low 1.5-mA

typical supply current per channel.

The TLE2682 features a shutdown pin (FB/SD), which can be used to disable the switched-capacitor section.

When disabled, the switched-capacitor voltage converter block draws less then 150 µA from the power supply,

VIN.

The switched-capacitor voltage converter block also provides an on-board regulator; with the addition of an

external divider, a well-regulated output voltage is easily obtained. The internal oscillator runs at a nominal

frequency of 25 kHz. This can be synchronized to an external clock signal or can be varied using an external

capacitor. A 2.5-V reference is brought out to VREF for use with the on-board regulator or external circuitry.

Additional filtering can be added to minimize switching noise.

The TLE2682 is characterized for operation over the industrial temperature range of −40°C to 85°C. This device

is available in a 16-pin wide-body surface-mount package.

AVAILABLE OPTION

PACKAGE

TA

SMALL OUTLINE

(DW)

−40°C to 85°C

TLE2682IDW

The DW package is available taped and reeled. Add

the suffix R to the device type, (i.e., TLE2682IDWR).

Copyright 1993, Texas Instruments Incorporated

���

������

��� �������!��� �" #$��%�! �" �� &$'(�#�!��� )�!%*

���)$#!" #������ !� "&%#���#�!���" &%� !+% !%��" �� �%,�" ��"!�$�%�!"

"!��)��) -�����!.* ���)$#!��� &��#%""��/ )�%" ��! �%#%""���(. ��#($)%

!%"!��/ �� �(( &����%!%�"*

•

POST OFFICE BOX 655303 DALLAS, TEXAS 75265

POST OFFICE BOX 1443 HOUSTON, TEXAS 77251−1443

•

1

��������

�� �

����

����

�����

��� ����������� ���������

���� �������

��������� ����� � ���������

SLOS127 − JUNE 1993

functional block diagram

1 OUT

1 IN −

1 IN +

VCC −

VOUT

VREF

OSC

VIN

Amplifier Block

1

2

3

16

15

_

+

_

14

2 OUT

2 IN −

+

4

13

5

12

6

11

SwitchedCapacitor

Block

7

8

10

9

ACTUAL DEVICE

COMPONENT COUNT

AMPLIFIER

BLOCK

Transistors

Resistors

Diodes

Capacitors

2

VCC +

SWITCHEDCAPACITOR BLOCK

57

37

5

11

Transistors

Resistors

Diodes

Capacitors

•

71

44

2

5

POST OFFICE BOX 655303 DALLAS, TEXAS 75265

POST OFFICE BOX 1443 HOUSTON, TEXAS 77251−1443

•

2 IN +

CAP −

GND

CAP +

FB/SD

��������

�� �

����

����

�����

��� ����������� ���������

���� �������

��������� ����� � ���������

SLOS127 − JUNE 1993

absolute maximum ratings over operating free-air temperature range (unless otherwise noted)†

Supply voltage, VIN (see Note 1) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 16 V

Supply voltage, VCC + (see Note 2) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 16 V

Supply voltage, VCC − (see Note 2) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . −16 V

Differential input voltage, VID (see Note 3) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 32 V

Input voltage, VI (any input of amplifier) (see Note 2) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . VCC ±

Input voltage range, VI (FB/SD) (see Note 1) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 0 V to VIN

Input voltage range, VI (OSC) (see Note 1) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 0 V to VREF

Input current, II (each input of amplifier) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . ± 1 mA

Output current, IO (each output of amplifier) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . ± 80 mA

Total current into VCC + . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 160 mA

Total current out of VCC − . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 160 mA

Duration of short-circuit current at (or below) TA = 25°C (see Note 4) (each amplifier) . . . . . . . . . . . unlimited

Continuous total dissipation . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . See Dissipation Rating Table

Junction temperature (see Note 5) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 150°C

Operating free-air temperature range, TA . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . −40°C to 85°C

Storage temperature range . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . −65°C to 150°C

Lead temperature 1,6 mm (1/16 inch) from case for 10 seconds . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 260°C

† Stresses beyond those listed under “absolute maximum ratings” may cause permanent damage to the device. These are stress ratings only, and

functional operation of the device at these or any other conditions beyond those indicated under “recommended operating conditions” is not

implied. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

NOTES: 1. Voltage values are with respect to the switched-capacitor block GND pin.

2. Voltage values, except differential voltages, are with respect to the midpoint between VCC+ and VCC− .

3. Differential voltages are at IN+ with respect to IN −.

4. The output may be shorted to either supply. Temperature and/or supply voltages must be limited to ensure that the maximum

dissipation rating is not exceeded.

5. The devices are functional up to the absolute maximum junction temperature.

DISSIPATION RATING TABLE

PACKAGE

TA ≤ 25°C

POWER RATING

DERATING FACTOR

ABOVE TA = 25°C

TA = 70°C

POWER RATING

TA = 85°C

POWER RATING

DW

1025 mW

8.2 mW/°C

656 mW

533 mW

recommended operating conditions

Supply voltage, VCC + / VIN

Common-mode input voltage, VIC

VCC ± = ± 5 V

VCC ± = ± 15 V

Output current at VOUT, IO

Operating free-air temperature, TA

•

POST OFFICE BOX 655303 DALLAS, TEXAS 75265

POST OFFICE BOX 1443 HOUSTON, TEXAS 77251−1443

•

MIN

MAX

3.5

15

UNIT

V

−1

5

−11

15

0

100

mA

−40

85

°C

V

3

��������

�� �

����

����

�����

��� ����������� ���������

���� �������

��������� ����� � ���������

SLOS127 − JUNE 1993

OPERATIONAL AMPLIFIER SECTION

electrical characteristics at specified free-air temperature, VCC± = ±5 V (unless otherwise noted)

PARAMETER

TEST CONDITIONS

VIO

Input offset voltage

αVIO

Temperature coefficient of input offset voltage

IIO

Input offset current

IIB

Input bias current

VIC = 0,

RS = 50 Ω

VO = 0,

TA†

25°C

25°C

VO = 0,

2.4

25

5

100

950

25°C

15

Full range

RS = 50 Ω

Common-mode input voltage range

IO = − 200 µA

VOM + Maximum positive peak output voltage swing

IO = − 2 mA

IO = − 20 mA

IO = 200 µA

VOM − Maximum negative peak output voltage swing

IO = 2 mA

IO = 20 mA

Large-signal differential voltage amplification

VO = ± 2.3 V

5

to

−1

5

to

−0.8

25°C

3.8

Full range

3.7

25°C

3.5

Full range

3.4

25°C

1.5

Full range

1.5

25°C

−3.8

Full range

−3.7

25°C

−3.5

Full range

−3.4

25°C

−1.5

Full range

−1.5

RL = 600 Ω

25°C

75

Full range

74

25°C

85

RL = 2 kΩ

Full range

84

25°C

90

RL = 10 kΩ

Full range

89

Input resistance

VIC = 0

25°C

ci

Input capacitance

VIC = 0,

See Figure 5

zo

Open-loop output impedance

f = 1 MHz

25°C

70

CMRR Common-mode rejection ratio

VIC = VICRmin,

RS = 50 Ω

25°C

Full range

68

kSVR

Supply-voltage rejection ratio (∆VCC

CC± /∆VIO)

VCC ± = ± 5 V to ± 15 V,

VO = 0

RS = 50 Ω

25°C

82

Full range

80

ICC

Supply current (both channels)

VO = 0,

No load

25°C

2.7

ax

Crosstalk attenuation

VIC = 0,

RL = 2 kΩ

25°C

IOS

Short-circuit output current

VO = 0

VID = 1 V

VID = − 1 V

25°C

•

•

pA

2

nA

V

3.9

V

2.3

−4.2

−4.1

V

−2.4

91

100

dB

106

25°C

11

25°C

2.5

POST OFFICE BOX 655303 DALLAS, TEXAS 75265

POST OFFICE BOX 1443 HOUSTON, TEXAS 77251−1443

µV/°C

4.1

Differential

† Full range is − 40°C to 85°C.

mV

pA

5

to

−1.9

Common mode

VO = 0,

UNIT

175

Ω

1012

ri

4

7.5

Full range

Full range

AVD

MAX

0.9

9

Full range

VIC = 0,

See Figure 4

TYP

Full range

25°C

25

C

VICR

MIN

pF

Ω

80

89

dB

99

2.9

Full range

dB

3.6

3.6

120

mA

dB

−35

45

mA

��������

�� �

����

����

�����

��� ����������� ���������

���� �������

��������� ����� � ���������

SLOS127 − JUNE 1993

operating characteristics at specified free-air temperature, VCC± = ±5 V

PARAMETER

SR +

Positive slew rate

SR −

Negative slew rate

TA†

25°C

TEST CONDITIONS

VO(PP) = ± 2.3 V,

RL = 2 kΩ,

AVD = − 1,

CL = 100 pF,

See Figure 1

Full range

Settling time

To 10 mV

f = 10 kHz

RS = 20 Ω,

See Figure 3

VN(PP)

In

Peak-to-peak equivalent input noise voltage

V/ s

V/µs

38

V/ s

V/µs

20

µss

0.4

28

25°C

f = 10 Hz to

10 kHz

f = 0.1 Hz to

10 Hz

UNIT

0.25

To 1 mV

Equivalent input noise voltage

MAX

35

25°C

f = 10 Hz

Vn

TYP

20

25°C

Full range

AVD = − 1,

2-V step,

RL = 1 kΩ,

CL = 100 pF

MIN

11.6

nV/√Hz

6

µV

V

25°C

0.6

Equivalent input noise current

VIC = 0,

f = 10 kHz

25°C

THD + N

Total harmonic distortion plus noise

VO(PP) = 5 V,

f = 1 k Hz,

RS = 25Ω

AVD = 10,

RL = 2 kΩ,

kΩ

2.8

25°C

B1

Unity-gain bandwidth

VI = 10 mV,

CL = 25 pF,

RL = 2 kΩ,

See Figure 2

25°C

9.4

MHz

BOM

Maximum output-swing bandwidth

VO(PP) = 4 V,

RL = 2 kΩ,

AVD = − 1,

CL = 25 pF

25°C

2.8

MHz

φm

Phase margin at unity gain

VI = 10 mV,

CL = 25 pF,

RL = 2 kΩ,

See Figure 2

25°C

56°

fA/√Hz

0.013%

† Full range is 40°C to 85°C.

•

POST OFFICE BOX 655303 DALLAS, TEXAS 75265

POST OFFICE BOX 1443 HOUSTON, TEXAS 77251−1443

•

5

��������

�� �

����

����

�����

��� ����������� ���������

���� �������

��������� ����� � ���������

SLOS127 − JUNE 1993

electrical characteristics at specified free-air temperature, VCC ± = ±15 V (unless otherwise noted)

PARAMETER

TEST CONDITIONS

VIO

Input offset voltage

αVIO

Temperature coefficient of input offset voltage

VIC = 0,

RS = 50 Ω

VO = 0,

TA†

25°C

MIN

Input offset current

IIB

Input bias current

VICR

VO = 0,

2.4

25

6

100

Full range

950

25°C

20

25°C

15 to

−11

Full range

15 to

−10.8

RS = 50 Ω

Common-mode input voltage range

IO = − 200 µA

A

25°C

13.8

Full range

13.7

25°C

13.5

IO = − 2 mA

Full range

13.4

25°C

11.5

IO = − 20 mA

VOM − Maximum negative peak output voltage swing

Full range

11.5

IO = 200 µA

A

25°C

−13.8

Full range

−13.7

25°C

−13.5

IO = 2 mA

Full range

−13.4

25°C

−11.5

Full range

−11.5

IO = 20 mA

25°C

75

Full range

74

25°C

90

RL = 2 kΩ

Full range

89

25°C

90

RL = 10 kΩ

Full range

89

RL = 600 Ω

Large-signal differential voltage amplification

VO = ± 10 V

ri

Input resistance

VIC = 0

ci

Input capacitance

VIC = 0,

See Figure 5

zo

Open-loop output impedance

f = 1 MHz

96

109

dB

118

80

VCC ± = ± 5 V to ± 15 V,

VO = 0,

RS = 50 Ω

ICC

Supply current (both channels)

VO = 0,

No load

ax

Crosstalk attenuation

VIC = 0,

RL = 2 kΩ

25°C

IOS

Short-circuit output current

VO = 0

VID = 1 V

VID = − 1 V

25°C

† Full range is − 40°C to 85°C.

•

−12.4

25°C

Supply-voltage rejection ratio (∆VCC±

CC /∆VIO)

POST OFFICE BOX 655303 DALLAS, TEXAS 75265

POST OFFICE BOX 1443 HOUSTON, TEXAS 77251−1443

•

V

2.5

kSVR

25°C

82

Full range

80

25°C

2.7

V

−14

7.5

79

nA

−14.2

25°C

Full range

pA

2.5

12.3

25°C

80

pA

V

Differential

25°C

µV/°C

13.9

Common mode

VO = 0,

mV

14.1

1012

VIC = VICRmin,

RS = 50 Ω

UNIT

175

15 to

−11.9

25°C

CMRR Common-mode rejection ratio

6

7.5

Full range

VOM + Maximum positive peak output voltage swing

AVD

1.1

9

Full range

VIC = 0,

See Figure 4

MAX

Full range

25°C

IIO

TYP

Ω

pF

Ω

98

dB

99

dB

3.1

Full range

3.6

3.6

120

−30

−45

30

48

mA

dB

mA

��������

�� �

����

����

�����

��� ����������� ���������

���� �������

��������� ����� � ���������

SLOS127 − JUNE 1993

operating characteristics at specified free-air temperature, VCC± = ±15 V

PARAMETER

SR +

SR −

TEST CONDITIONS

Positive slew rate

VO(PP) = ± 10 V,

AVD = − 1,

CL = 100 pF,

Negative slew rate

AVD = − 1,

10-V step,

RL = 1 kΩ,

CL = 100 pF

Settling time

RL = 2 kΩ,

See Figure 1

TA†

25°C

MIN

TYP

25

40

Full range

20

25°C

25

Full range

20

To 10 mV

f = 10 kHz

RS = 20 Ω,

See Figure 3

VN(PP)

In

45

V/ s

V/µs

0.4

µss

To 1 mV

Equivalent input noise voltage

1.5

28

25°C

11.6

f = 10 Hz to

10 kHz

Peak-to-peak equivalent input noise voltage

f = 0.1 Hz to

10 Hz

UNIT

V/ s

V/µs

25°C

f = 10 Hz

Vn

MAX

nV/√Hz

6

µV

V

25°C

0.6

Equivalent input noise current

VIC = 0,

f = 10 kHz

25°C

2.8

THD + N

Total harmonic distortion plus noise

VO(PP) = 20 V,

f = 1 kHz,

RS = 25Ω

AVD = 10,

RL = 2 kΩ,

25°C

0.008%

B1

Unity-gain bandwidth

VI = 10 mV,

CL = 25 pF,

RL = 2 kΩ,

See Figure 2

25°C

8

10

MHz

BOM

Maximum output-swing bandwidth

VO(PP) = 20 V,

RL = 2 kΩ,

AVD = − 1,

CL = 25 pF

25°C

478

637

kHz

φm

Phase margin at unity gain

VI = 10 mV,

CL = 25 pF,

RL = 2 kΩ,

See Figure 2

25°C

fA/√Hz

57°

† Full range is − 40°C to 85°C.

•

POST OFFICE BOX 655303 DALLAS, TEXAS 75265

POST OFFICE BOX 1443 HOUSTON, TEXAS 77251−1443

•

7

��������

�� �

����

����

�����

��� ����������� ���������

���� �������

��������� ����� � ���������

SLOS127 − JUNE 1993

SWITCHED-CAPACITOR SECTION

electrical characteristics over recommended supply voltage range (unless otherwise noted)

VCC = 5 V, TJ =25°C,

VCC = 7 V, TJ =25°C,

VCC = 5 V to 15 V,

RL(VOUT) = 500 Ω,

See Note 6

TA‡

25°C

RL(VOUT) = 500 Ω,

See Note 7

25°C

RL(VOUT) = 500 Ω,

See Note 6

Full range

7

27

VCC = 7 V to 12 V,

VCC = 5 V,

RL(VOUT) = 500 Ω,

See Note 7

Full range

5

25

RL(VOUT) = 100 Ω to 500 Ω

Full range

20

140

VCC = 7 V,

RL(VOUT) = 100 Ω to 500 Ω

Full range

20

70

TEST CONDITIONS†

PARAMETER

Regulated output voltage,

VOUT

Input regulation

Output regulation

MIN

TYP

MAX

−3.75

−4

−4.25

−4.7

−5

−5.2

Voltage loss, VCC − VOUT

(see Note 8)

VCC = 7 V,

CIN = COUT = 100-µF tantalum

IO = 10 mA

IO = 100 mA

Full range

0.35

0.55

Full range

1.1

1.8

Output resistance

∆IO = 10 mA to 100 mA,

See Note 9

Full range

Oscillator frequency

Iref = 50 µA

A

Reference voltage, Vref

A

Iref = 60 µA

VCC = 7 V,

V

mV

mV

V

10

15

Ω

15

25

35

kHz

25°C

2.35

2.5

2.65

Full range

2.25

25°C

2.35

Full range

2.25

Full range

VCC = 5 V,

UNIT

2.75

2.5

2.65

V

2.75

Maximum switch current

25°C

300

mA

† Data applies for the switched-capacitor block only. Amplifier block is not connected.

‡ Full range is − 40°C to 85°C.

NOTES: 6. Regulation specifications are for the switched-capacitor section connected as a positive to negative converter / regulator

(see Figure 105) with R1 = 23.7 kΩ, R2 = 102.2 kΩ, CIN = 10 µF (tantalum), COUT = 100 µF (tantalum), and C1 = 0.002 µF.

7. Regulation specifications are for the switched-capacitor section connected as a positive to negative converter/regulator

(see Figure 105) with R1 = 20 kΩ, R2 = 102.5 kΩ, CIN = 10 µF (tantalum), COUT = 100 µF (tantalum) and C1 = 0.002 µF.

8. For voltage-loss tests, the switched-capacitor section is connected as a voltage inverter, with VREF , OSC, and FB/SD (pins 6, 7,

and 9) unconnected. The voltage losses may be higher in other configurations.

9. Output resistance is defined as the slope of the curve (∆VO vs ∆IO) for output currents of 10 mA to 100 mA. This represents the linear

portion of the curve. The incremental slope of the curve are higher at currents less than 10 mA due to the characteristics of the switch

transistors.

AMPLIFIER AND SWITCHED-CAPACITOR SECTIONS CONNECTED

electrical characteristics, VIN = VCC+ = 5 V, TA = 25°C (see Figure 6)

PARAMETER

TEST CONDITIONS

VOM + Maximum positive peak output voltage swing

VOM − Maximum negative peak output voltage swing

Voltage loss, VIN − | VOUT | (see Note 8)

MIN

TYP

RL = 10 kΩ

4.1

RL = 600 Ω

3.6

RL = 100 Ω

2.3

RL = 10 kΩ

−3.9

RL = 600 Ω

−3.3

RL = 100 Ω

−1.9

VID = − 100 mV,

CIN = COUT = 100-µF tantalum

RL = 10 kΩ

0.55

RL = 600 Ω

0.65

RL = 100 Ω

0.9

MAX

UNIT

V

V

V

NOTE 8: For voltage-loss tests, the switched-capacitor section is connected as a voltage inverter, with VREF , OSC, and FB/SD (pins 6, 7,

and 9) unconnected. The voltage losses may be higher in other configurations.

8

•

POST OFFICE BOX 655303 DALLAS, TEXAS 75265

POST OFFICE BOX 1443 HOUSTON, TEXAS 77251−1443

•

��������

�� �

����

����

�����

��� ����������� ���������

���� �������

��������� ����� � ���������

SLOS127 − JUNE 1993

supply current (no load), TA = 25°C

PARAMETER

TEST CONDITIONS

Supply current

VCC+ = 5 V,

VCC+ = 5 V,

Supply current in shutdown

VIN = 5 V,

VIN = 5 V,

MIN

VFB/SD = 2.5 V,

VFB/SD = 0 V

TYP

VO = 0

MAX

UNIT

8.9

mA

2.5

mA

PARAMETER MEASUREMENT INFORMATION

10 kΩ

2 kΩ

VCC +

VCC +

2 kΩ

VI

−

+

VCC −

VI

VO

RL

−

+

† Includes fixture capacitance

Figure 2. Unity-Gain Bandwidth

and Phase-Margin Test Circuit

Figure 1. Slew-Rate Test Circuit

2 kΩ

Ground Shield

VCC +

−

+

RS

CL†

VCC −

RL

CL†

† Includes fixture capacitance

RS

VO

100 Ω

VCC +

−

+

VO

VO

VCC −

Picoammeters

VCC −

Figure 4. Input-Bias and

Offset-Current Test Circuit

Figure 3. Noise-Voltage Test Circuit

VCC +

IN −

−

Cid

IN +

Cic

VO

+

Cic

VCC −

Figure 5. Internal Input Capacitance

•

POST OFFICE BOX 655303 DALLAS, TEXAS 75265

POST OFFICE BOX 1443 HOUSTON, TEXAS 77251−1443

•

9

��������

�� �

����

����

�����

��� ����������� ���������

���� �������

��������� ����� � ���������

SLOS127 − JUNE 1993

PARAMETER MEASUREMENT INFORMATION

typical values

Typical values presented in this data sheet represent the median (50% point) of device parametric performance.

input bias and offset current

At the picoampere bias-current level typical of the TLE2682, accurate measurement of the bias currents

becomes difficult. Not only does this measurement require a picoammeter, but test socket leakages can easily

exceed the actual device bias currents. To accurately measure these small currents, Texas Instruments uses

a two-step process. The socket leakage is measured using picoammeters with bias voltages applied, but with

no device in the socket. The device is then inserted in the socket, and a second test is performed that measures

both the socket leakage and the device input bias current (see Figure 6). The two measurements are then

subtracted algebraically to determine the bias current of the device.

RL

1

VCC +

1 OUT

2

1 IN −

2 OUT

1 IN +

2 IN −

3

4

2 IN +

VCC −

1N4933

+

0.1 µF

VOUT

CAP −

VREF

GND

OSC

CAP +

VIN

FB/SD

6

7

8

Figure 6. Bias-Current Test Circuit

10

•

POST OFFICE BOX 655303 DALLAS, TEXAS 75265

POST OFFICE BOX 1443 HOUSTON, TEXAS 77251−1443

•

15

14

5V

0.1 µF

RL

13

TLE2682

5

COUT

16

12

11

CIN

+

10

9

+

2 µF

��������

�� �

����

����

�����

��� ����������� ���������

���� �������

��������� ����� � ���������

SLOS127 − JUNE 1993

TYPICAL CHARACTERISTICS

Table of Graphs for Operational Amplifier Section

FIGURE

VIO

αVIO

Input offset voltage

Distribution

7

Temperature coefficient of input offset voltage

Distribution

8

IIO

Input offset current

vs Free-air temperature

9, 10

IIB

Input bias current

vs Free-air temperature

vs Supply voltage

9, 10

11

VIC

VID

Common-mode input voltage range

vs Free-air temperature

12

Differential input voltage

vs Output voltage

13, 14

VOM +

Maximum positive peak output voltage

vs Output current

vs Free-air temperature

vs Supply voltage

15

17, 18

19

VOM −

Maximum negative peak output voltage

vs Output current

vs Free-air temperature

vs Supply voltage

16

17, 18

19

VO(PP)

Maximum peak-to-peak output voltage

vs Frequency

20

VO

Output voltage

vs Settling time

21

AVD

Large-signal differential voltage amplification

vs Load resistance

vs Free-air temperature

vs Frequency

22

23, 24

25, 26

CMRR

Common-mode rejection ratio

vs Frequency

vs Free-air temperature

27

28

kSVR

Supply voltage rejection ratio

vs Frequency

vs Free-air temperature

29

30

ICC

Supply current

vs Supply voltage

vs Free-air temperature

vs Differential input voltage

IOS

Short-circuit output current

vs Supply voltage

vs Time

vs Free-air temperature

SR

Slew rate

vs Free-air temperature

vs Load resistance

vs Differential input voltage

Vn

Equivalent input noise voltage

vs Frequency

42

Input-referred noise voltage

vs Noise bandwidth

Over a 10-second time interval

43

44

Third-octave spectral noise density

vs Frequency

45

THD + N

Total harmonic distortion plus noise

vs Frequency

46, 47

B1

Unity-gain bandwidth

vs Load capacitance

48

Gain-bandwidth product

vs Free-air temperature

vs Supply voltage

49

50

Gain margin

vs Load capacitance

51

Phase margin

vs Free-air temperature

vs Supply voltage

vs Load capacitance

52

53

54

Phase shift

vs Frequency

Vn

Am

φm

•

POST OFFICE BOX 655303 DALLAS, TEXAS 75265

POST OFFICE BOX 1443 HOUSTON, TEXAS 77251−1443

•

31

32

33, 34

35

36

37

38, 39

40

41

25, 26

11

��������

�� �

����

����

�����

��� ����������� ���������

���� �������

��������� ����� � ���������

SLOS127 − JUNE 1993

TYPICAL CHARACTERISTICS

Table of Graphs for Operational Amplifier Section (Continued)

FIGURE

Large-signal pulse response, noninverting

vs Time

55

Small-signal pulse response

vs Time

56

zo

Output impedance

vs Frequency

57

ax

Crosstalk attenuation

vs Frequency

58

Table of Graphs for Switched-Capacitor Section

FIGURE

ICC

fosc

Iavg

VO

∆VREF

12

Shutdown threshold voltage

vs Free-air temperature

59

Supply current

vs Input voltage

60

Oscillator frequency

vs Free-air temperature

61

Supply current in shutdown

vs Input voltage

62

Average supply current

vs Output current

63

Output voltage loss

vs Input capacitance

Output voltage loss

vs Oscillator frequency

65, 66

Regulated output voltage

vs Free-air temperature

67

Reference voltage change

vs Free-air temperature

68

Voltage loss

vs Output current

69

•

POST OFFICE BOX 655303 DALLAS, TEXAS 75265

POST OFFICE BOX 1443 HOUSTON, TEXAS 77251−1443

•

64

��������

�� �

����

����

�����

��� ����������� ���������

���� �������

��������� ����� � ���������

SLOS127 − JUNE 1993

TYPICAL CHARACTERISTICS†

OPERATIONAL AMPLIFIER SECTION

DISTRIBUTION OF TLE2682 INPUT OFFSET

VOLTAGE TEMPERATURE COEFFICIENT

DISTRIBUTION OF TLE2682

INPUT OFFSET VOLTAGE

30

20

Percentage of Units − %

16

27

Percentage of Amplifiers − %

18

600 Units Tested From One Wafer Lot

VCC ± = ± 15 V

TA = 25°C

14

12

10

8

6

24

21

18

15

12

9

4

6

2

3

0

−4

− 2.4

− 0.8

2.4

0.8

310 Amplifiers

VCC ± = ± 15 V

TA = − 40 to 85°C

0

− 24 −18

4

−12

−6

Figure 7

IIB

I IO − Input Bias and Input Offset Currents − nA

IIB and IIO

IIB

I IO − Input Bias and Input Offset Currents − nA

IIB and IIO

VCC ± = ± 5 V

VIC = 0

VO = 0

1

0.1

IIB

IIO

0.01

−35

−15

5

12

18

24

30

INPUT BIAS CURRENT AND

INPUT OFFSET CURRENT

vs

FREE-AIR TEMPERATURE

100

0.001

−55

6

Figure 8

INPUT BIAS CURRENT AND

INPUT OFFSET CURRENT

vs

FREE-AIR TEMPERATURE

10

0

αVIO − Temperature Coefficient − µV/°C

VIO

V IO − Input Offset Voltage − mV

25

45

65

85

100

10

VCC ± = ± 15 V

VIC = 0

VO = 0

1

IIB

0.1

IIO

0.01

0.001

−55

−35

TA − Free-Air Temperature − °C

Figure 9

25

45

65

−15

5

TA − Free-Air Temperature − °C

85

Figure 10

† Data applies to the operational amplifier block only. Switched-capacitor block is not supplying VCC − supply.

•

POST OFFICE BOX 655303 DALLAS, TEXAS 75265

POST OFFICE BOX 1443 HOUSTON, TEXAS 77251−1443

•

13

��������

�� �

����

����

�����

��� ����������� ���������

���� �������

��������� ����� � ���������

SLOS127 − JUNE 1993

TYPICAL CHARACTERISTICS†

OPERATIONAL AMPLIFIER SECTION

INPUT BIAS CURRENT

vs

SUPPLY VOLTAGE

COMMON-MODE INPUT VOLTAGE RANGE

vs

TEMPERATURE

10 6

VIC − Common-Mode Input Voltage Range − V

VIC

VCC + + 0.5

VICmax = VCC +

IIIB

IB − Input Bias Current − pA

10 5

TA = 85°C

VICmin

10 4

10 3

10 2

TA = 25°C

10

TA = − 40°C

5

10

15

20

25

30

VCC +

VICmax

VCC + − 0.5

VCC − + 3.5

VICmin

VCC − + 3

VCC − + 2.5

VCC − + 2

−55

1

0

RS = 50 Ω

35

−35

−15

Figure 11

400

RL = 600 Ω

100

RL = 2 kΩ

RL = 10 kΩ

RL = 10 kΩ

− 100

RL = 2 kΩ

− 200

− 300

RL = 600 Ω

−3

−2

VCC ± = ± 15 V

VIC = 0

RS = 50 Ω

TA = 25°C

300

V

VID

µV

ID − Differential Input Voltage − uV

V

VID

ID − Differential Input Voltage − uV

µV

VCC ± = ± 5 V

VIC = 0

RS = 50 Ω

TA = 25°C

− 400

−5 −4

−1

0

1

2

3

4

200

RL = 2 kΩ

100

0

RL = 10 kΩ

RL = 10 kΩ

− 100

RL = 2 kΩ

− 200

− 300

− 400

− 15

5

RL = 600 Ω

RL = 600 Ω

− 10

−5

0

5

VO − Output Voltage − V

VO − Output Voltage − V

Figure 13

Figure 14

† Data applies to the operational amplifier block only. Switched-capacitor block is not supplying VCC − supply.

14

85

DIFFERENTIAL INPUT VOLTAGE

vs

OUTPUT VOLTAGE

400

0

65

Figure 12

DIFFERENTIAL INPUT VOLTAGE

vs

OUTPUT VOLTAGE

200

45

TA − Free-Air Temperature − °C

VCC − Total Supply Voltage (Referred to VCC − ) − V

300

25

5

•

POST OFFICE BOX 655303 DALLAS, TEXAS 75265

POST OFFICE BOX 1443 HOUSTON, TEXAS 77251−1443

•

10

15

��������

�� �

����

����

�����

��� ����������� ���������

���� �������

��������� ����� � ���������

SLOS127 − JUNE 1993

TYPICAL CHARACTERISTICS†

OPERATIONAL AMPLIFIER SECTION

MAXIMUM NEGATIVE PEAK OUTPUT VOLTAGE

vs

OUTPUT CURRENT

V OM − − Maximum Negative Peak Output Voltage − V

VVOM

OM+ − Maximum Positive Peak Output Voltage − V

MAXIMUM POSITIVE PEAK OUTPUT VOLTAGE

vs

OUTPUT CURRENT

15

13.5

12

TA = − 40°C

10.5

9

7.5

TA = 25°C

6

4.5

TA = 85°C

3

1.5

VCC ± = ± 15 V

0

0

− 15

− 13.5

TA = − 40°C

− 12

− 10.5

TA = 25°C

−9

− 7.5

−6

TA = 85°C

− 4.5

−3

− 1.5

VCC ± = ± 15 V

0

0

− 5 −10 −15 − 20 − 25 − 30 − 35 − 40 − 45 − 50

5

10

IO − Output Current − mA

Figure 15

| V OM | − Maximum Peak Output Voltage − V

VOM − Maximum Peak Output Voltage − V

V

OM

IO = − 2 mA

IO = − 20 mA

1

VCC ± = ± 5 V

0

−1

IO = 20 mA

−2

−3

IO = 2 mA

−4

−5

−55

IO = 200 µA

−35

−15

5

25

30

35

40

45

50

15

4

2

25

MAXIMUM PEAK OUTPUT VOLTAGE

vs

FREE-AIR TEMPERATURE

IO = − 200 µA

3

20

Figure 16

MAXIMUM PEAK OUTPUT VOLTAGE

vs

FREE-AIR TEMPERATURE

5

15

IO − Output Current − mA

45

65

14.5

14

IO = 2 mA

IO = − 2 mA

13.5

13

IO = 20 mA

12.5

IO = − 20 mA

12

11.5

11

10.5

10

− 55

85

IO = 200 µA

IO = − 200 µA

VCC ± = ± 15 V

− 35

TA − Free-Air Temperature − °C

− 15

5

25

45

65

85

TA − Free-Air Temperature − °C

Figure 17

Figure 18

† Data applies to the operational amplifier block only. Switched-capacitor block is not supplying VCC − supply.

•

POST OFFICE BOX 655303 DALLAS, TEXAS 75265

POST OFFICE BOX 1443 HOUSTON, TEXAS 77251−1443

•

15

��������

�� �

����

����

�����

��� ����������� ���������

���� �������

��������� ����� � ���������

SLOS127 − JUNE 1993

TYPICAL CHARACTERISTICS†

OPERATIONAL AMPLIFIER SECTION

MAXIMUM PEAK OUTPUT VOLTAGE

vs

SUPPLY VOLTAGE

MAXIMUM PEAK-TO-PEAK OUTPUT VOLTAGE

vs

FREQUENCY

V O(PP) − Maximum Peak-to-Peak Output Voltage − V

VO(PP)

25

VOM

VOM − Maximum Peak Output Voltage − V

TA = 25°C

20

IO = − 200 µA

15

10

IO = − 2 mA

5

IO = − 20 mA

0

IO = 20 mA

−5

IO = 200 µA

−10

IO = 2 mA

−15

− 20

− 25

0

2.5

5

7.5

10

12.5

15

17.5

30

VCC ± = ± 15 V

25

20

TA = − 40°C

15

10

TA = 25°C,

85°C

VCC ± = ± 5 V

5

0

100 k

TA = − 40°C

1M

400 k

2M

f − Frequency − Hz

200 k

|VCC ± | − Supply Voltage − V

10 M

LARGE-SIGNAL DIFFERENTIAL

VOLTAGE AMPLIFICATION

vs

LOAD RESISTANCE

OUTPUT VOLTAGE

vs

SETTLING TIME

125

12.5

10

AVD

AVD − Large-Signal Differential

Voltage Amplification − dB

10 mV

7.5

VO

VO − Output Voltage − V

4M

Figure 20

Figure 19

1mV

5

2.5

VCC ± = ± 15 V

RL = 1 kΩ

CL = 100 pF

AV = − 1

TA = 25°C

Rising

0

Falling

− 2.5

−5

ÁÁ

ÁÁ

ÁÁ

1mV

− 7.5

10 mV

− 10

0

0.5

1

1.5

120

VIC = 0

RS = 50 Ω

TA = 25°C

115

110

VCC ± = ± 15 V

105

2

VCC ± = ± 5 V

100

95

90

0.1

− 12.5

Settling Time − µs

1

10

RL − Load Resistance − kΩ

Figure 21

Figure 22

† Data applies to the operational amplifier block only. Switched-capacitor block is not supplying VCC − supply.

16

RL = 2 kΩ

TA = 25°C,

85°C

•

POST OFFICE BOX 655303 DALLAS, TEXAS 75265

POST OFFICE BOX 1443 HOUSTON, TEXAS 77251−1443

•

100

��������

�� �

����

����

�����

��� ����������� ���������

���� �������

��������� ����� � ���������

SLOS127 − JUNE 1993

TYPICAL CHARACTERISTICS†

OPERATIONAL AMPLIFIER SECTION

ÁÁ

ÁÁ

LARGE-SIGNAL DIFFERENTIAL

VOLTAGE AMPLIFICATION

vs

FREE-AIR TEMPERATURE

110

125

107

121

RL = 10 kΩ

104

AVD

AVD − Large-Signal Differential

Voltage Amplification − dB

AVD

AVD − Large-Signal Differential

Voltage Amplification − dB

LARGE-SIGNAL DIFFERENTIAL

VOLTAGE AMPLIFICATION

vs

FREE-AIR TEMPERATURE

101

RL = 2 kΩ

98

95

92

89

86

83

VCC ± = ± 5 V

VO = ± 2.3 V

80

− 55

− 35

−15

5

117

113

25

105

101

RL = 600 Ω

97

93

89

85

− 55

65

45

RL = 2 kΩ

109

ÁÁ

ÁÁ

RL = 600 Ω

VCC ± = ± 15 V

VO = ± 10 V

RL = 10 kΩ

− 35

TA − Free-Air Temperature − °C

−15

5

25

45

65

85

TA − Free-Air Temperature − °C

Figure 23

Figure 24

SMALL-SIGNAL DIFFERENTIAL VOLTAGE

AMPLIFICATION AND PHASE SHIFT

vs

FREQUENCY

140

0°

ÁÁ

ÁÁ

ÁÁ

Gain

100

80

20°

40°

60°

Phase Shift

60

80°

40

100°

20

120°

0

140°

− 20

160°

− 40

Phase Shift

AVD

A

vd − Small-Signal Differential

Voltage Amplification − dB

120

VCC ± = ± 15 V

RL = 2 kΩ

CL = 100 pF

TA = 25°C

180°

1

10

100

1k

10 k 100 k 1 M

10 M 100 M

f − Frequency − Hz

Figure 25

† Data applies to the operational amplifier block only. Switched-capacitor block is not supplying VCC − supply.

•

POST OFFICE BOX 655303 DALLAS, TEXAS 75265

POST OFFICE BOX 1443 HOUSTON, TEXAS 77251−1443

•

17

��������

�� �

����

����

�����

��� ����������� ���������

���� �������

��������� ����� � ���������

SLOS127 − JUNE 1993

TYPICAL CHARACTERISTICS†

OPERATIONAL AMPLIFIER SECTION

SMALL-SIGNAL DIFFERENTIAL VOLTAGE

AMPLIFICATION AND PHASE SHIFT

vs

FREQUENCY

30

80°

ÁÁ

ÁÁ

Phase Shift

20

100°

CL = 25 pF

10

120°

Gain

0

140°

Phase Shift

AVD

A

vd − Small-Signal Differential

Voltage Amplification − dB

CL = 100 pF

CL = 100 pF

VCC ±= ± 15 V

VIC = 0

RC = 2 kΩ

TA = 25°C

− 10

CL = 25 pF

180°

100

− 20

2

1

4

20

10

160°

40

f − Frequency − MHz

Figure 26

COMMON-MODE REJECTION RATIO

vs

FREQUENCY

COMMON-MODE REJECTION RATIO

vs

FREE-AIR TEMPERATURE

100

CMRR − Common-Mode Rejection Ratio − dB

CMRR − Common-Mode Rejection Ratio − dB

100

VCC ± = ± 15 V

90

VCC ± = ± 5 V

80

70

60

50

40

30

VIC = 0

VO = 0

RS = 50 Ω

TA = 25°C

20

10

0

10

100

1k

10 k

100 k

1M

97

VCC ± = ± 15 V

94

91

88

VCC ± = ± 5 V

85

82

79

76

73

VIC = VICRmin

VO = 0

RS = 50 Ω

70

− 55

10 M

− 35

−15

5

Figure 27

Figure 28

† Data applies to the operational amplifier block only. Switched-capacitor block is not supplying VCC − supply.

18

25

45

TA − Free-Air Temperature − °C

f − Frequency − Hz

•

POST OFFICE BOX 655303 DALLAS, TEXAS 75265

POST OFFICE BOX 1443 HOUSTON, TEXAS 77251−1443

•

65

85

��������

�� �

����

����

�����

��� ����������� ���������

���� �������

��������� ����� � ���������

SLOS127 − JUNE 1993

TYPICAL CHARACTERISTICS†

OPERATIONAL AMPLIFIER SECTION

SUPPLY-VOLTAGE REJECTION RATIO

vs

FREQUENCY

SUPPLY-VOLTAGE REJECTION RATIO

vs

FREE-AIR TEMPERATURE

120

kXXXX

SVR − Supply-Voltage Rejection Ratio − dB

kXXXX

SVR − Supply-Voltage Rejection Ratio − dB

120

kSVR +

100

80

60

kSVR −

40

20

∆ VCC ± = ± 5 V to ± 15 V

VIC = 0

VO = 0

RS = 50 Ω

TA = 25°C

0

− 20

10

100

1k

10 k

100 k

1M

114

kSVR +

108

102

96

90

kSVR −

84

78

72

66

VIC = 0

VO = 0

RS = 50 Ω

60

− 55

10 M

− 35

f − Frequency − Hz

−15

Figure 29

45

65

85

65

85

SUPPLY CURRENT

vs

FREE-AIR TEMPERATURE

4

3.5

VIC = 0

VO = 0

No Load

3.4

3.6

VIC = 0

VO = 0

No Load

3.3

3.4

IICC

CC − Supply Current − mA

IICC

CC − Supply Current − mA

25

Figure 30

SUPPLY CURRENT

vs

SUPPLY VOLTAGE

3.8

5

TA − Free-Air Temperature − °C

TA = 85°C

3.2

3

TA = 25°C

2.8

2.6

TA = − 40°C

3.2

3

2.8

2.7

2.2

2.6

0

2.5

5

7.5

10

12.5

15

2.5

− 55

17.5

VCC ± = ± 5 V

2.9

2.4

2

VCC ± = ± 15 V

3.1

− 35

− 15

5

25

45

TA − Free-Air Temperature − °C

|VCC ±| − Supply Voltage − V

Figure 32

Figure 31

† Data applies to the operational amplifier block only. Switched-capacitor block is not supplying VCC − supply.

•

POST OFFICE BOX 655303 DALLAS, TEXAS 75265

POST OFFICE BOX 1443 HOUSTON, TEXAS 77251−1443

•

19

��������

�� �

����

����

�����

��� ����������� ���������

���� �������

��������� ����� � ���������

SLOS127 − JUNE 1993

TYPICAL CHARACTERISTICS†

OPERATIONAL AMPLIFIER SECTION

SUPPLY CURRENT

vs

DIFFERENTIAL INPUT VOLTAGE

SUPPLY CURRENT

vs

DIFFERENTIAL INPUT VOLTAGE

14

25

VCC + = 5 V

VCC − = 0

VIC = + 4.5 V

TA = 25°C

Open Loop

No Load

10

VCC ± = ± 15 V

VIC = 0

TA = 25°C

Open Loop

No Load

20

IICC

CC − Supply Current − mA

IICC

CC − Supply Current − mA

12

8

6

4

15

10

5

2

0

− 0.5

− 0.25

0

0.25

VID − Differential Input Voltage − V

0

− 1.5

0.5

−1

Figure 33

48

40

IIOS

OS − Short-Circuit Output Current − mA

IOS

I OS − Short-Circuit Output Current − mA

50

VID = − 1 V

24

12

VO = 0

TA = 25°C

−12

− 24

VID = 1 V

− 36

− 48

− 60

0

2.5

5

7.5

10

1

1.5

12.5

15

VID = − 1 V

30

20

10

VCC ± = ± 15 V

VO = 0

TA = 25°C

0

−10

− 20

− 30

VID = 1 V

− 40

− 50

17.5

0

|VCC ± | − Supply Voltage − V

60

120

t − Elapsed Time − s

Figure 35

Figure 36

† Data applies to the operational amplifier block only. Switched-capacitor block is not supplying VCC − supply.

20

0.5

SHORT-CIRCUIT OUTPUT CURRENT

vs

TIME

60

0

0

Figure 34

SHORT-CIRCUIT OUTPUT CURRENT

vs

SUPPLY VOLTAGE

36

− 0.5

VID − Differential Input Voltage − V

•

POST OFFICE BOX 655303 DALLAS, TEXAS 75265

POST OFFICE BOX 1443 HOUSTON, TEXAS 77251−1443

•

180

��������

�� �

����

����

�����

��� ����������� ���������

���� �������

��������� ����� � ���������

SLOS127 − JUNE 1993

TYPICAL CHARACTERISTICS†

OPERATIONAL AMPLIFIER SECTION

SHORT-CIRCUIT OUTPUT CURRENT

vs

FREE-AIR TEMPERATURE

SLEW RATE

vs

FREE-AIR TEMPERATURE

45

64

VCC ± = ± 15 V

48

32

41

VCC ± = ± 5 V

16

− 16

VCC ± = ± 5 V

VID = 1 V

− 32

VCC ± = ± 15 V

− 48

− 64

− 35

39

SR −

37

35

SR +

33

31

29

27

VO = 0

− 80

− 55

VCC ± = ± 5 V

RL = 2 kΩ

CL = 100 pF

43

VID = − 1 V

SR − Slew Rate − V/xs

V/µ s

IIOS

OS − Short-Circuit Output Current − mA

80

−15

5

25

45

65

25

− 55

85

− 35

−15

Figure 37

65

85

50

VCC ± = ± 15 V

RL = 2 kΩ

CL = 100 pF

40

Rising Edge

30

SR − Slew Rate − V/µ s

SR − Slew Rate − V/µ s

45

SLEW RATE

vs

LOAD RESISTANCE

70

62

25

Figure 38

SLEW RATE

vs

FREE-AIR TEMPERATURE

66

5

TA − Free-Air Temperature − °C

TA − Free-Air Temperature − °C

58

54

50

SR −

46

42

SR +

20

10

VCC ± = ± 5 V

VO ± = ± 2.5 V

0

−10

AV = − 1

CL = 100 pF

TA = 25°C

− 20

38

− 30

34

− 40

30

− 55

Falling Edge

− 50

100

1k

− 35

−15

5

25

45

65

85

VCC ± = ± 15 V

VO ± = ± 10 V

10 k

100 k

RL − Load Resistance − Ω

TA − Free-Air Temperature − °C

Figure 39

Figure 40

† Data applies to the operational amplifier block only. Switched-capacitor block is not supplying VCC − supply.

•

POST OFFICE BOX 655303 DALLAS, TEXAS 75265

POST OFFICE BOX 1443 HOUSTON, TEXAS 77251−1443

•

21

��������

�� �

����

����

�����

��� ����������� ���������

���� �������

��������� ����� � ���������

SLOS127 − JUNE 1993

TYPICAL CHARACTERISTICS†

OPERATIONAL AMPLIFIER SECTION

SLEW RATE

vs

DIFFERENTIAL INPUT VOLTAGE

EQUIVALENT INPUT NOISE VOLTAGE

vs

FREQUENCY

50

50

Hz

AV = − 1

SR − Slew Rate − V/µ s

30

V n − Equivalent Input Noise Voltage − nV/

Vn

40

AV = 1

Rising Edge

20

VCC ± = ± 15 V

VO ± = ± 10 V (10% − 90%)

CL = 100 pF

TA = 25°C

10

0

−10

− 20

Falling Edge

− 30

AV = − 1

− 40

AV = 1

− 50

0.1

0.4

1

4

VCC ± = ± 15 V

VIC = 0

RS = 20 Ω

TA = 25°C

45

40

35

30

25

20

15

10

5

0

10

10

100

Figure 41

1.2

Vn − Input-Referred Noise Voltage − µV

Vn

Vn − Input-Referred Noise Voltage − µV

Vn

INPUT-REFERRED NOISE VOLTAGE

OVER A 10-SECOND TIME INTERVAL

VCC ± = ± 15 V

VIC = 0

RS = 20 Ω

TA = 25°C

10

Peak-to-Peak

1

RMS

0.1

10

100

1k

10 k

0.9

100 k

VCC ± = ± 15 V

f = 0.1 to 10 Hz

TA = 25°C

0.6

0.3

0

− 0.3

− 0.6

0

0.01

1

1

2

3

4

5

6

t − Time − s

f − Frequency − Hz

Figure 44

Figure 43

† Data applies to the operational amplifier block only. Switched-capacitor block is not supplying VCC − supply.

22

10 k

Figure 42

INPUT-REFERRED NOISE VOLTAGE

vs

NOISE BANDWIDTH

100

1k

f − Frequency − Hz

VID − Differential Input Voltage − V

•

POST OFFICE BOX 655303 DALLAS, TEXAS 75265

POST OFFICE BOX 1443 HOUSTON, TEXAS 77251−1443

•

7

8

9

10

��������

�� �

����

����

�����

��� ����������� ���������

���� �������

��������� ����� � ���������

SLOS127 − JUNE 1993

TYPICAL CHARACTERISTICS†

OPERATIONAL AMPLIFIER SECTION

TOTAL HARMONIC DISTORTION PLUS

NOISE

vs

FREQUENCY

THIRD-OCTAVE SPECTRAL NOISE DENSITY

vs

FREQUENCY

Start Frequency: 12.5 Hz

Stop Frequency: 20 kHz

VCC ± = ± 15 V

VIC = 0

TA = 25°C

− 80

− 85

Noise − dB

THD + N − Total Harmonic Distortion + Noise − %

− 75

− 90

− 95

− 100

− 105

− 110

− 115

10

15

20

25

30

40

35

45

1

AV = 100, RL = 600 Ω

0.1

AV = 100, RL = 2 kΩ

AV = 10, RL = 600 Ω

AV = 10, RL = 2 kΩ

0.01

VCC ± = ± 5 V

VO = 5 VPP

TA = 25°C

Filter: 10 Hz to 500-kHz Band Pass

0.001

10

100

Figure 45

UNITY GAIN BANDWIDTH

vs

LOAD CAPACITANCE

Filter: 10 Hz to 500-kHz Band Pass

VCC ± = ± 15 V

VO = 20 VPP

TA = 25°C

B1

B1 − Unity Gain Bandwidth − MHz

THD + N − Total Harmonic Distortion + Noise − %

13

1

AV = 100, RL = 600 Ω

AV = 100, RL = 2 kΩ

AV = 10, RL = 600 Ω

AV = 10, RL = 2 kΩ

0.001

10

100 k

Figure 46

TOTAL HARMONIC DISTORTION PLUS NOISE

vs

FREQUENCY

0.01

10 k

f − Frequency − Hz

Frequency Bands

0.1

1k

VCC ± = ± 15 V

VIC = 0

VO = 0

RL = 2 kΩ

TA = 25°C

12

11

10

9

8

7

100

1k

10 k

0

100 k

20

40

60

80

100

CL − Load Capacitance − pF

f − Frequency − Hz

Figure 47

Figure 48

† Data applies to the operational amplifier block only. Switched-capacitor block is not supplying VCC − supply.

•

POST OFFICE BOX 655303 DALLAS, TEXAS 75265

POST OFFICE BOX 1443 HOUSTON, TEXAS 77251−1443

•

23

��������

�� �

����

����

�����

��� ����������� ���������

���� �������

��������� ����� � ���������

SLOS127 − JUNE 1993

TYPICAL CHARACTERISTICS†

OPERATIONAL AMPLIFIER SECTION

GAIN-BANDWIDTH PRODUCT

vs

SUPPLY VOLTAGE

GAIN-BANDWIDTH PRODUCT

vs

FREE-AIR TEMPERATURE

13

f = 100 kHz

VIC = 0

VO = 0

RL = 2 kΩ

CL = 100 pF

12

Gain-Bandwidth Product − MHz

Gain-Bandwidth Product − MHz

13

11

VCC ± = ± 15 V

10

9

VCC ± = ± 5 V

8

7

− 55

f = 100 kHz

VIC = 0

VO = 0

RL = 2 kΩ

CL = 100 pF

TA = 25°C

12

11

10

9

8

7

− 35

−15

5

25

65

45

0

85

5

TA − Free-Air Temperature − °C

Figure 49

20

15

Figure 50

PHASE MARGIN

vs

TEMPERATURE

GAIN MARGIN

vs

LOAD CAPACITANCE

90°

10

VCC ± = ± 15 V

VIC = 0

VO = 0

RL = 2 kΩ

TA = 25°C

80°

VIC = 0

VO = 0

RL = 2 kΩ

70°

xm

φ m − Phase Margin

8

Gain Margin − dB

10

VCC+± | − Supply Voltage − V

|VCC

6

4

VCC ± = ± 15 V

CL = 25 pF

60°

50°

VCC ± = ± 15 V

VCC ± = ± 5 V

40°

30°

CL = 100 pF

VCC ± = ± 5 V

20°

2

10°

0°

− 55

0

0

20

40

60

80

100

− 35

−15

5

CL − Load Capacitance − pF

Figure 52

Figure 51

† Data applies to the operational amplifier block only. Switched-capacitor block is not supplying VCC − supply.

24

25

45

TA − Free-Air Temperature − °C

•

POST OFFICE BOX 655303 DALLAS, TEXAS 75265

POST OFFICE BOX 1443 HOUSTON, TEXAS 77251−1443

•

65

85

��������

�� �

����

����

�����

��� ����������� ���������

���� �������

��������� ����� � ���������

SLOS127 − JUNE 1993

TYPICAL CHARACTERISTICS†

OPERATIONAL AMPLIFIER SECTION

PHASE MARGIN

vs

LOAD CAPACITANCE

90°

90°

80°

80°

70°

70°

CL = 25 pF

60°

xm

φ m − Phase Margin

xm

φ m − Phase Margin

PHASE MARGIN

vs

SUPPLY VOLTAGE

50°

CL = 100 pF

40°

30°

10°

VCC ± = ± 15 V

50°

VCC ± = ± 5 V

40°

30°

VIC = 0

VO = 0

RL = 2 kΩ

TA = 25°C

20°

VIC = 0

VO = 0

RL = 2 kΩ

TA = 25°C

20°

60°

10°

0°

0°

0

4

8

12

0

16

20

40

60

80

100

CL − Load Capacitance − pF

|VCC ±| − Supply Voltage − V

Figure 53

Figure 54

NONINVERTING LARGE-SIGNAL

PULSE RESPONSE

SMALL-SIGNAL PULSE RESPONSE

15

100

TA = 25°C,

85°C

TA = − 40°C

5

VO

VO − Output Voltage − mV

VO

VO − Output Voltage − V

10

TA = − 40°C

0

TA = 25°C,

85°C

−5

VCC ± = ± 15 V

AV = 1

RL = 2 kΩ

CL = 100 pF

− 10

− 15

0

1

2

3

t − Time − µs

4

50

0

VCC ± = ± 15 V

AV = − 1

RL = 2 kΩ

CL = 100 pF

TA = 25°C

− 50

− 100

5

0

Figure 55

0.4

0.8

t − Time − µs

1.2

1.6

Figure 56

† Data applies to the operational amplifier block only. Switched-capacitor block is not supplying VCC − supply.

•

POST OFFICE BOX 655303 DALLAS, TEXAS 75265

POST OFFICE BOX 1443 HOUSTON, TEXAS 77251−1443

•

25

��������

�� �

����

����

�����

��� ����������� ���������

���� �������

��������� ����� � ���������

SLOS127 − JUNE 1993

TYPICAL CHARACTERISTICS†

OPERATIONAL AMPLIFIER SECTION

CLOSED-LOOP OUTPUT IMPEDANCE

vs

FREQUENCY

CROSSTALK ATTENUATION

vs

FREQUENCY

140

VCC ± = ± 15 V

TA = 25°C

10

120

a

axx − Crosstalk Attenuation − dB

zo− Output Impedance − XΩ

zo

100

AV = 100

1

AV = 10

0.1

AV = 1

0.01

100

1k

10 k

100 k

1M

80

60

40

VCC ± = ± 15 V

VIC = 0

RL = 2 kΩ

TA = 25°C

20

10

0.001

10

100

10 M

100

1k

f − Frequency − Hz

f − Frequency − Hz

Figure 57

Figure 58

† Data applies to the operational amplifier block only. Switched-capacitor block is not supplying VCC − supply.

26

•

POST OFFICE BOX 655303 DALLAS, TEXAS 75265

POST OFFICE BOX 1443 HOUSTON, TEXAS 77251−1443

•

10 k

100 k

��������

�� �

����

����

�����

��� ����������� ���������

���� �������

��������� ����� � ���������

SLOS127 − JUNE 1993

TYPICAL CHARACTERISTICS†

SWITCHED-CAPACITOR SECTION

SHUTDOWN THRESHOLD VOLTAGE

vs

FREE-AIR TEMPERATURE

SUPPLY CURRENT

vs

INPUT VOLTAGE

0.6

5

4

VFB/SD

I CC − Supply Current − mA

Shutdown Threshold Voltage − V

IO = 0

0.5

0.4

0.3

0.2

2

1

0.1

0

− 50

3

0

0

25

50

75

− 25

TA − Free-Air Temperature − °C

100

0

2.5

Figure 59

7.5

5

10

VCC − Input Voltage − V

12.5

15

Figure 60

SUPPLY CURRENT IN SHUTDOWN

vs

INPUT VOLTAGE

OSCILLATOR FREQUENCY

vs

FREE-AIR TEMPERATURE

120

35

Supply Current in Shutdown − µA

f osc − Oscillator Frequency − kHz

33

31

29

VCC = 15 V

27

25

VCC = 3.5 V

23

21

19

100

VFB/SD = 0

80

60

40

20

17

15

− 50

0

0

25

50

75

−25

TA − Free-Air Temperature − °C

0

100

2.5

5

7.5

10

VCC − Input Voltage − V

12.5

15

Figure 62

Figure 61

† Data applies to the switched-capacitor block only. Amplifier block is not connected.

•

POST OFFICE BOX 655303 DALLAS, TEXAS 75265

POST OFFICE BOX 1443 HOUSTON, TEXAS 77251−1443

•

27

��������

�� �

����

����

�����

��� ����������� ���������

���� �������

��������� ����� � ���������

SLOS127 − JUNE 1993

TYPICAL CHARACTERISTICS†

SWITCHED-CAPACITOR SECTION

OUTPUT VOLTAGE LOSS

vs

INPUT CAPACITANCE

140

1.4

120

1.2

IO = 100 mA

Output Voltage Loss − V

I avg − Average Supply Current − mA

AVERAGE SUPPLY CURRENT

vs

OUTPUT CURRENT

100

80

60

40

1.0

0.8

IO = 50 mA

0.6

IO = 10 mA

0.4

Inverter Configuration

COUT = 100-µF Tantalum

fosc = 25 kHz

0.2

20

0

0

0

20

40

60

80

0

100

IO − Output Current − mA

10

20 30 40 50 60 70 80

CIN − Input Capacitance − µF

Figure 63

Figure 64

OUTPUT VOLTAGE LOSS

vs

OSCILLATOR FREQUENCY

OUTPUT VOLTAGE LOSS

vs

OSCILLATOR FREQUENCY

2.5

2.5

Inverter Configuration

CIN = 10-µF Tantalum

COUT = 100-µF Tantalum

2.25

2

Output Voltage Loss − V

Output Voltage Loss − V

1.75

1.5

IO = 100 mA

1.25

1

IO = 50 mA

0.75

0.5

1.75

1.5

1.25

1

IO = 50 mA

0.75

0.25

0.25

0

0

2

4

7 10

20

40

fosc − Oscillator Frequency − kHz

IO = 100 mA

0.5

IO = 10 mA

1

Inverter Configuration

CIN = 100-µF Tantalum

COUT = 100-µF Tantalum

2.25

2

IO = 10 mA

1

100

10

2

4

20

40

fosc − Oscillator Frequency − kHz

Figure 66

Figure 65

† Data applies to the switched-capacitor block only. Amplifier block is not connected.

28

90 100

•

POST OFFICE BOX 655303 DALLAS, TEXAS 75265

POST OFFICE BOX 1443 HOUSTON, TEXAS 77251−1443

•

100

��������

�� �

����

����

�����

��� ����������� ���������

���� �������

��������� ����� � ���������

SLOS127 − JUNE 1993

TYPICAL CHARACTERISTICS†

SWITCHED-CAPACITOR SECTION

REGULATED OUTPUT VOLTAGE

vs

FREE-AIR TEMPERATURE

REFERENCE VOLTAGE CHANGE

vs

FREE-AIR TEMPERATURE

100

∆V REF − Reference Voltage Change − mV

VO − Regulated Output Voltage − V

− 4.7

− 4.8

− 4.9

VCC = 7 V

−5

− 5.1

−11.6

−11.8

VCC = 15 V

−12

−12.2

−12.4

−12.6

− 50

− 25

0

25

50

75

TA − Free-Air Temperature − °C

80

60

40

20

0

− 20

VREF @ 25°C = 2.5 V

− 40

− 60

− 80

− 100

− 50

100

− 25

0

25

50

75

TA − Free-Air Temperature − °C

Figure 67

100

Figure 68

VOLTAGE LOSS

vs

OUTPUT CURRENT

2

3.5 V ≤ VCC ≤ 15 V

CIN = COUT = 100 µF

1.8

Voltage Loss − V

1.6

1.4

1.2

1

TA = 85°C

0.8

0.6

TA = 25°C

0.4

0.2

0

0

10

20

30 40 50 60 70

Output Current − mA

80

90 100

Figure 69

† Data applies to the switched-capacitor block only. Amplifier block is not connected.

•

POST OFFICE BOX 655303 DALLAS, TEXAS 75265

POST OFFICE BOX 1443 HOUSTON, TEXAS 77251−1443

•

29

��������

�� �

����

����

�����

��� ����������� ���������

���� �������

��������� ����� � ���������

SLOS127 − JUNE 1993

APPLICATION INFORMATION

amplifier section

input characteristics

The TLE2682 is specified with a minimum and a maximum input voltage that if exceeded at either input could

cause the device to malfunction.

Because of the extremely high input impedance and resulting low bias-current requirements, the TLE2682

operational amplifier section is well suited for low-level signal processing; however, leakage currents on printed

circuit boards and sockets can easily exceed bias-current requirements and cause degradation in system

performance. It is a good practice to include guard rings around inputs (see Figure 70). These guards should

be driven from a low-impedance source at the same voltage level as the common-mode input.

Unused amplifiers should be connected as grounded voltage followers to avoid potential oscillation.

VI

+

+

VI

+

VO

VO

−

−

VO

−

VI

Figure 70. Use of Guard Rings

switched-capacitor section

Figure 71 shows the functional block diagram for the switched-capacitor block only.

VCC

VREF

2.5 V

REF

R

Drive

+

CAP +

−

FB/SD

CIN†

Q

OSC

OSC

Q

CAP −

Drive

R

Drive

GND

COUT†

VOUT

Drive

† External capacitors

Figure 71. Functional Block Diagram for Switched-Capacitor Block Only

30

•

POST OFFICE BOX 655303 DALLAS, TEXAS 75265

POST OFFICE BOX 1443 HOUSTON, TEXAS 77251−1443

•

��������

�� �

����

����

�����

��� ����������� ���������

���� �������

��������� ����� � ���������

SLOS127 − JUNE 1993

APPLICATION INFORMATION

The TLE2682 high-speed JFET-input amplifiers are ideal for conditioning fast signals from high-impedance sources.

When interfacing with ADCs in single-supply 5-V systems, its on board charge pump provides the negative rail

necessary for reliable operation of the JFET inputs and delivers a common-mode input voltage range that includes

ground and the positive rail. The amplifiers can also drive resistive loads to 0.000 V while sinking 25 mA.

Figure 72 shows the switched-capacitor section configured as a voltage inverter generating approximately − 5-V

supply voltage from the single 5-V supply available. Three external components are necessary: the storage

capacitors, CIN and COUT, and a fast recovery Schottky diode to clamp VOUT during start-up. The diode is necessary

because the amplifiers present a load referenced to the positive rail and tend to pull VOUT above ground, which may

prevent the switched-capacitor section from starting (see section on pin functions). The amplifiers use the 5-V supply

for VCC+ (pin 16) and the derived −5-V supply for VCC − (pin 4). One amplifier is shown driving an ADC; the other is

driving a resistive load (see Figure 73).

RL

5V

To ADC

RF

RF

Signal

From

Preamplifier

1

2

3

4

5

Filter

1N4933

COUT

+

6

7

8

1 OUT

VCC+

1 IN −

2 OUT

1 IN+

2 IN −

VCC −

2 IN+

VOUT

CAP −

VREF

GND

OSC

CAP+

VIN

FB/SD

16

15

RF

RIN

14

13

Signal

From

Transducer

12

CIN

11

+

10

9

Shutdown

Figure 72. Switched-Capacitor Block Supplying Negative Rail for Amplifiers

•

POST OFFICE BOX 655303 DALLAS, TEXAS 75265

POST OFFICE BOX 1443 HOUSTON, TEXAS 77251−1443

•

31

��������

�� �

����

����

�����

��� ����������� ���������

���� �������

��������� ����� � ���������

SLOS127 − JUNE 1993

APPLICATION INFORMATION

5V

RF

RF

RIN

Signal

From

Preamplifier

Signal

From

Transducer

−

+

RIN

To ADC

−

+

AMP1

AMP2

RL

VIN

VOUT

Voltage

Converter

Shutdown

FB/SD

VREF

Figure 73. Equivalent Schematic: Amplifier 1 Driving Resistive Load,

Amplifier 2 Interfacing to an ADC

Using the switched-capacitor network to generate the negative rail for the amplifiers (or other circuitry) requires

special design considerations to minimize the effects of ripple and switching noise. Using larger values for COUT and

selecting low-ESR capacitors reduces the ripple and noise present on VOUT, the − 5-V rail (refer to the capacitor

section and the output ripple discussion in the switched-capacitor section). Figure 74 and Figure 75 show the

smoothing effect of changing COUT from 10 µF to 100 µF when VOUT is supplying 1 mA. Figure 76 and Figure 77

demonstrate that at heavier loads the ripple and noise are more pronounced and while increasing the size of COUT

helps, other steps may be necessary.

RIPPLE AND SWITCHING NOISE ON

SWITCHED-CAPACITOR OUTPUT

vs

TIME

RIPPLE AND SWITCHING NOISE ON

SWITCHED-CAPACITOR OUTPUT

vs

TIME

80

20

VCC+ = 5 V

IL = 1 mA

CIN = 100 µF

COUT = 10 µF

40

15

Ripple and Switching Noise on

Switched-Capacitor Output − mV

Ripple and Switching Noise on

Switched-Capacitor Output − mV

60

20

0

−20

−40

−60

VCC+ = 5 V

IL = 1 mA

CIN = 100 µF

COUT = 100 µF

10

5

0

−5

−10

−15

−80

0

10

20

30

40

50

60

70

80

−20

0

90 100

10

t − Time − µs

30

40

50

60

t − Time − µs

Figure 75

Figure 74

32

20

•

POST OFFICE BOX 655303 DALLAS, TEXAS 75265

POST OFFICE BOX 1443 HOUSTON, TEXAS 77251−1443

•

70

80

90 100

��������

�� �

����

����

�����

��� ����������� ���������

���� �������

��������� ����� � ���������

SLOS127 − JUNE 1993

APPLICATION INFORMATION

RIPPLE AND SWITCHING NOISE ON

SWITCHED-CAPACITOR OUTPUT

vs

TIME

RIPPLE AND SWITCHING NOISE ON

SWITCHED-CAPACITOR OUTPUT

vs

TIME

200

80

60

Ripple and Switching Noise on

Switched-Capacitor Output − mV

Ripple and Switching Noise on

Switched-Capacitor Output − mV

150

VCC+ = 5 V

IL = 10 mA

CIN = 100 µF

COUT = 100 µF

100

50

0

−50

−100

VCC+ = 5 V

IL = 10 mA

CIN = 100 µF

COUT = 10 µF

−150

−200

0

10

20

30

40

20

0

−20

−40

−60

40

50

60

70

80

−80

0

90 100

10

20

30

t − Time − µs

40

50

60

70

80

90 100

t − Time − µs

Figure 76

Figure 77

LH

VOUT

VCC

0.1 µF

COUT

CF

+

Filter

fr =

1

2π

LC

Figure 78. LC Filter Used to Reduce Ripple and Switching Noise,

fr = 1/2π √LC, A = −40 dB per Decade

A low-pass LC filter can be added to the circuit to further reduce ripple and noise. For example, adding a filter as shown

in Figure 78, implemented using a 50-µH inductor and 200-µF capacitor (available in surface mount), achieves the

following results (see Figure 79 through Figure 82).

•

POST OFFICE BOX 655303 DALLAS, TEXAS 75265

POST OFFICE BOX 1443 HOUSTON, TEXAS 77251−1443

•

33

��������

�� �

����

����

�����

��� ����������� ���������

���� �������

��������� ����� � ���������

SLOS127 − JUNE 1993

APPLICATION INFORMATION

RIPPLE AND SWITCHING NOISE ON

SWITCHED-CAPACITOR OUTPUT

vs

TIME

RIPPLE AND SWITCHING NOISE ON

SWITCHED-CAPACITOR OUTPUT

vs

TIME

20

20

10

15

Ripple and Switching Noise on

Switched-Capacitor Output − mV

Ripple and Switching Noise on

Switched-Capacitor Output − mV

15

VCC+ = 5 V

IL = 1 mA

CIN = 100 µF

COUT = 10 µF

Without Filter

5

0

−5

−10

−15

−20

0

10

20

30

40 50 60 70

t − Time − µs

80

10

5

0

−5

−10

−15

−20

0

90 100

VCC+ = 5 V

IL = 1 mA

CIN = 100 µF

COUT = 10 µF

Filter:

LF = 50 µH

CF = 220 µF

See Figure 78

10

20

15

Ripple and Switching Noise on

Switched-Capacitor Output − mV

Ripple and Switching Noise on

Switched-Capacitor Output − mV

70

80

90 100

20

VCC+ = 5 V

IL = 1 mA

CIN = 100 µF

COUT = 100 µF

Without Filter

5

0

−5

−10

10

VCC+ = 5 V

IL = 1 mA

CIN = 100 µF

COUT = 100 µF

5

0

−5

−10

−15

−15

Filter:

LF = 50 µH

CF = 220 µF

See Figure 78

−20

10

20

30

40 50 60 70

t − Time − µs

80

90 100

0

10

Figure 81

34

60

RIPPLE AND SWITCHING NOISE ON

SWITCHED-CAPACITOR OUTPUT

vs

TIME

20

−20

0

50

Figure 80

RIPPLE AND SWITCHING NOISE ON

SWITCHED-CAPACITOR OUTPUT

vs

TIME

10

40

t − Time − µs

Figure 79

15

30

20

30

40 50 60

t − Time − µs

Figure 82

•

POST OFFICE BOX 655303 DALLAS, TEXAS 75265

POST OFFICE BOX 1443 HOUSTON, TEXAS 77251−1443

•

70

80

90 100

��������

�� �

����

����

�����

��� ����������� ���������

���� �������

��������� ����� � ���������