2Gbit x8, x16: NAND Flash Memory

NAND Flash Memory

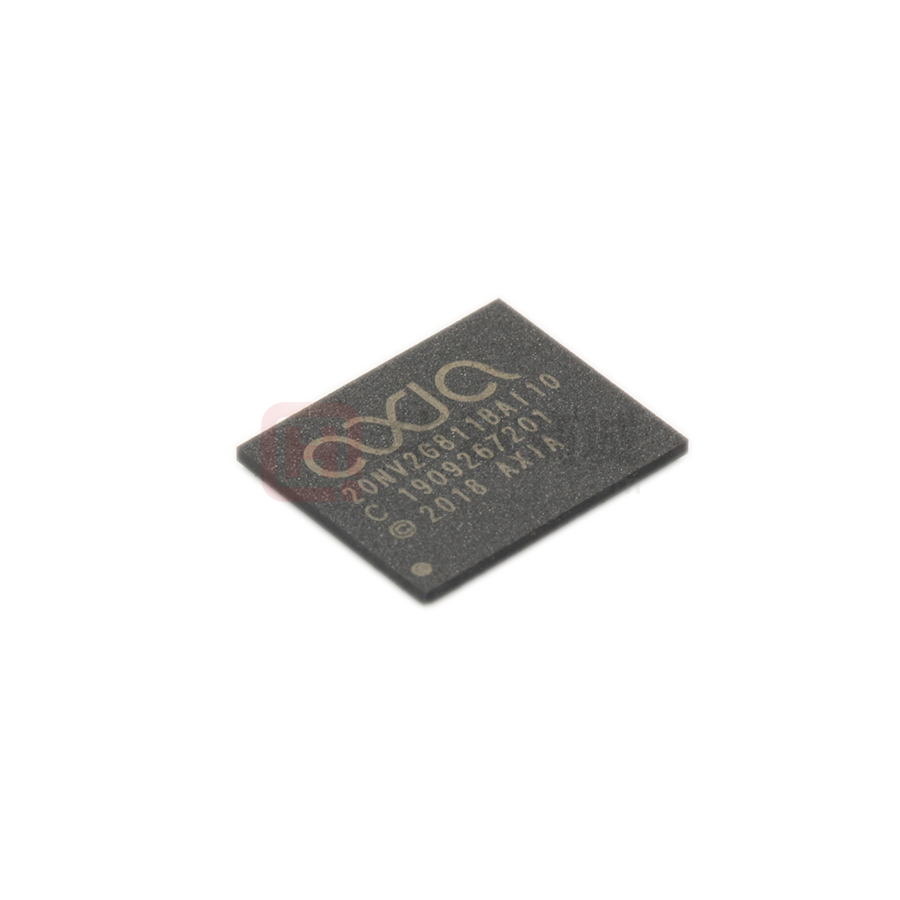

(AX20NV2G8, AX20NV2G6)

Features

•

•

•

•

•

•

•

•

Interface

▪ Open NAND Flash Interface

(ONFI 1.0) compliant

▪ x8, x16

Technology

▪ Single-level cell (SLC)

▪ 3xnm NAND Process

Operating Voltage Range

▪ VCC: 2.70V – 3.60V

Operating Temperature Range

▪ Industrial: -40°C to 85°C

Packages

▪ 48-pin TSOP (12.0mm x 20mm)

▪ 63-ball FBGA (9mm x 11mm)

Device Signature

▪ Manufacturer’s ID

▪ Device ID

▪ Device Parameters

▪ Unique ID

One Time Programmable Area (OTP)

▪ One Block (128K + 4K bytes)

Quality and Reliability

▪ Recommended Error Correction Code:

4-bit / 528 bytes of data

▪ Data retention: 10 years

▪ Endurance (P/E cycles): 100K (Typ.)

•

•

•

•

▪ Block zero (block address 00h) is a valid

block when shipped from factory and will

remain valid for at least 1K P/E cycles with

ECC

Memory Array Organization

▪ x8

• Page size: 2176 bytes

(2048 + 128 bytes)

▪ x16

• Page size: 1088 words

(1024 + 64 words)

▪ Block size: 64 pages

(128K + 8K bytes)

▪ Device size: 2048 blocks (2 Planes)

Data Protection

▪ WP# signal: write protect entire device

Device Status

▪ Ready/Busy# (R/B#) signal: hardware

method for detecting internal operation

completion status

Advanced Command Set

▪ Program page cache mode

▪ Read page cache mode

▪ Page data move (copy back):

▪ Internal data move

▪ Multi-plane Commands

Performance

Device Operation

Values

Units

30.0 (Maximum)

µs

300.0 (Typical)

µs

Block Erase

3.5 (Typical)

ms

Standby

10.0 (Typical)

µA

Read page

15.0 (Typical)

mA

Read page

Program Page

Revision: F

Axia Memory Technology

P a g e 1 | 62

�2Gbit x8, x16: NAND Flash Memory

Table of Contents

Features ...................................................................................................................................................... 1

Performance .............................................................................................................................................. 1

Table of Contents ..................................................................................................................................... 2

General Description................................................................................................................................. 3

Ordering Options ..................................................................................................................................... 4

Valid Combinations — Standard ...................................................................................................... 4

Signal Description and Assignment ................................................................................................... 5

Package Options ...................................................................................................................................... 6

48-Pin TSOP (Top View) ..................................................................................................................... 6

63-Ball FBGA (Balls Down, Top View) ............................................................................................ 7

Architecture ............................................................................................................................................... 8

Status Register ................................................................................................................................... 11

Bus Interface ........................................................................................................................................... 17

Standby ................................................................................................................................................. 17

Busy ....................................................................................................................................................... 17

Device Protection (Write Protect WP#) ........................................................................................ 17

Command Input .................................................................................................................................. 18

Address Input...................................................................................................................................... 18

Data Input ............................................................................................................................................. 19

Data Output.......................................................................................................................................... 20

Command Set...................................................................................................................................... 21

Device Initialization ............................................................................................................................... 53

Device Power-Down .............................................................................................................................. 55

Electrical Specifications....................................................................................................................... 56

Error Management ................................................................................................................................. 59

ECC Management................................................................................................................................... 60

Product Use Limitations....................................................................................................................... 61

Limited Warranty ................................................................................................................................ 61

Revision History ..................................................................................................................................... 62

Revision: F

Axia Memory Technology

P a g e 2 | 62

�2Gbit x8, x16: NAND Flash Memory

General Description

Axia Memory Technology’s AX20NV2Gx is a 3.0V 2Gbit NAND Flash organized as 2176 bytes × 64 pages

× 2048 blocks. All read and program operations are performed using a 2176-byte register; allowing data to

be transferred to and from the memory array in 2176-bytes increments. The erase operation is implemented

in a single block unit (2176 bytes × 64 pages).

Axia’s NAND Flash devices communicate through an asynchronous ONFI 1.0 compatible interface for highperformance I/O operations. It is a multiplexed 8-bit/16-bit bus (I/Ox) that transfers commands, address,

and data. There are five control signals used to implement the asynchronous data interface: CE#, CLE,

ALE, WE#, and RE#. Additional signals control hardware write protection (WP#) and monitor device status

(R/B#). This hardware interface creates a low pin-count device with a standard pinout that remains the

same in Axia’s NAND device family, enabling future upgrades to higher densities with no board redesign.

Additionally, Axia’s NAND Flash devices support a copy back function which optimizes management of

defective blocks. When a page program operation fails, the data already loaded in the page buffer can be

directly programmed to another page inside the same array section without the time-consuming serial data

insertion phase.

Also present in Axia’s NAND Flash devices is a cache read feature that increases the read throughput.

During cache reading, the device loads the new data in a cache register while the previous data is

transferred to the I/Os.

And finally, Axia’s NAND Flash devices provide special features listed below in Table 1:

Table 1: Special Features

#

1

2

Feature Description

One-Time Programmable Area

Unique Identifier

Revision: F

Details

Size: 1 block (128K + 8K bytes)

Size: 16 bytes

Axia Memory Technology

P a g e 3 | 62

�2Gbit x8, x16: NAND Flash Memory

Ordering Options

The ordering part numbers are firmed by a valid combination of the following options:

AX 20 N V 2G 8 1 1 TA I 10 1

Packing Type

1: Tray

2: Tape & Reel

Special Features

10: MID Value 1

Temperature Range

C: 0°C to +85°C

I: -40°C to +85°C

E: -40°C to +105°C

Package Type

BA: 63-ball WFBGA (9x11x1.0)

TA: 48-pin TSOP

Die Code

1

NAND Generation

1: 1st Generation SLC

Bus Width

8: x8

6: x16

Density

2G: 2Gigabit

Operational Voltage

V: 2.70V to 3.60V

E: 1.65V to 1.95V

NAND Grade

N: Standard

Product Family

20: ONFI NAND

Brand

AX: Axia Memory Technology

Valid Combinations — Standard

Valid Combinations list includes device configurations currently available. Contact your local sales

office to confirm availability of specific valid combinations and to check on newly released

combinations.

Table 2: Valid Combinations List

Valid Combinations

Base Part

Number

AX20NV2G

Bus

Width

x8

Generation

1

Die

Code

1

Package

type

BA, TA

Temperature

Range

I

Special

Features

10

Packing

Type

1, 2

Part

Number

AX20NV2G811BAI101

AX20NV2G811TAI101

AX20NV2G811BAI102

Revision: F

Axia Memory Technology

P a g e 4 | 62

�2Gbit x8, x16: NAND Flash Memory

Signal Description and Assignment

Figure 1: Device Pinout

ALE

CE#

WP#

RE#

WE#

AXIA

I/O[x:0]

x: 7/15

NAND

2 Gbit

CLE

R/B#

Table 3: Signal Description

Signal

Type

CE#

CLE

Input

Input

ALE

Input

WE#

Input

RE#

WP#

Input

Input

R/B#

Output

I/O [7:0] - x8

I/O [15:0] - x16

Input / Output

VCC

Supply

VCC: Core and I/O power supply.

VSS

Supply

VSS: Core and I/O ground supply.

NC

DNU

Revision: F

Description

Chip enable: Enables or disables the NAND Flash.

Command latch enable: Loads a command from x8 - I/O[7:0], x16 - I/O[15:0] into the

command register.

Address latch enable: Loads an address from x8 - I/O[7:0], x16 - I/O[15:0] into the

address register.

Write enable: Transfers commands, addresses, and serial data from the host system to

the NAND Flash.

Read enable: Transfers serial data from the NAND Flash to the host system.

Write protect: Enables or disables array PROGRAM and ERASE operations.

Ready/Busy: An open-drain, active-low output that requires an external pull-up resistor.

This signal indicates NAND Flash activity.

Data inputs/outputs: The bidirectional I/Os transfer address, data, and command

information.

No connect: NCs are not internally connected. They can be driven (VCC / VSS) or left

unconnected.

Do not use: DNUs must be left unconnected.

Axia Memory Technology

P a g e 5 | 62

�2Gbit x8, x16: NAND Flash Memory

Package Options

48-Pin TSOP (Top View)

48

1

48

1

NC

text

text

NC

NC

text

text

VSS

NC

text

text

NC

NC

text

text

IO15

NC

text

text

NC

NC

text

text

IO14

NC

text

text

NC

NC

text

text

IO13

NC

text

text

IO7

NC

text

text

IO7

NC

text

text

IO6

NC

text

text

IO6

R/B#

text

text

IO5

R/B#

text

text

IO5

RE#

text

text

IO4

RE#

text

text

IO4

CE#

text

text

NC

CE#

text

text

IO12

NC

text

text

NC

NC

text

text

NC

NC

text

text

NC

NC

text

text

NC

VCC

text

12

37

text

VCC

VCC

text

12

37

text

VCC

VSS

text

13

36

text

VSS

VSS

text

13

36

text

NC

NC

text

text

NC

NC

text

text

NC

NC

text

text

NC

NC

text

text

NC

CLE

text

text

NC

CLE

text

text

IO11

ALE

text

text

IO3

ALE

text

text

IO3

WE#

text

text

IO2

WE#

text

text

IO2

WP#

text

text

IO1

WP#

text

text

IO1

NC

text

text

IO0

NC

text

text

IO0

NC

text

text

NC

NC

text

text

IO10

NC

text

text

NC

NC

text

text

IO9

NC

text

text

NC

NC

text

text

IO8

NC

text

text

NC

NC

text

text

VSS

Revision: F

48-Pin

TSOP

Package

(x8)

24

25

48-Pin

TSOP

Package

(x16)

24

Axia Memory Technology

25

P a g e 6 | 62

�2Gbit x8, x16: NAND Flash Memory

63-Ball FBGA (Balls Down, Top View)

Revision: F

Axia Memory Technology

P a g e 7 | 62

�2Gbit x8, x16: NAND Flash Memory

Architecture

Axia’s NAND Flash devices use ONFI 1.0 compatible interface for all operations. Data, commands, and

addresses are multiplexed onto the I/O pins. The commands received at the I/Os are latched by a command

register and are used to determine the operations the device must perform. The addresses are latched into

an address register and sent either to a row decoder to select a row address, or to a column decoder to

select a column address. Data is transferred to or from the NAND Flash memory array either in a byte

format (x8) or in a word format (x16) through a page buffer which is a combination of a data register and a

cache register. During normal page operations, the data and cache registers act as a single register. During

cache operations, the data and cache registers operate independently to increase data throughput. The

NAND Flash memory array is programmed and read using page-based operations and is erased using

block-based operations. The status register reports the status of all operations.

Figure 2: Functional Block Diagram

x8

IO[7:0]

x16

IO[15:0]

Address Register

Status Register

I/O

Control

Column

Decoder

ALE

CE#

WP#

RE#

CLE

WE#

R/B#

Row Decoder

Command Register

Command

&

Control

High Voltage Generator

NAND

Memory

Array

(2 Planes)

OTP Area

RDY_BSY#

Page Buffer

Revision: F

Axia Memory Technology

P a g e 8 | 62

�2Gbit x8, x16: NAND Flash Memory

Memory Array Architecture & Addressing

Figure 3: Memory Array Architecture

Plane of Even Numbered

Blocks

Plane of Odd Numbered

Blocks

x8:

Page = 2,048 + 128 bytes = 2,176 bytes

1 block = 64 pages (139,264 bytes)

2Gbit Device = 2048 blocks (285,212,672 bytes)

x16:

Page = 1,024 + 64 words = 1,088 words

1 block = 64 pages (69,632 words)

2Gbit Device = 2048 blocks (142,606,336 words)

Block 0

Block 1

Block 2

Block 3

Block 2044

Block 2045

Block 2046

Block 2047

Data Buffer

Data Buffer

Cache Buffer

Cache Buffer

Page

Buffer

x8 –

x16 –

x8 –

x16 –

Bytes

Words

x8 –

x16 –

Bytes

Words

x8 –

x16 –

Bytes

Words

Bytes

Words

Table 4: Array Addressing Sequence – x8, x16

x8:

Cycle

IO[7]

IO[6]

IO[5]

IO[4]

IO[3]

IO[2]

IO[1]

IO[0]

First

BYTA7

BYTA6

BYTA5

BYTA4

BYTA3

BYTA2

BYTA1

BYTA0

Second

Logic '0'

Logic '0'

Logic '0'

Logic '0'

BYTA11

BYTA10

BYTA9

BYTA8

Third

BA7

BA6 / PLA

PA5

PA4

PA3

PA2

PA1

PA0

Fourth

BA15

BA14

BA13

BA12

BA11

BA10

BA9

BA8

Logic '0'

Logic '0'

Logic '0'

Logic '0'

Logic '0'

Logic '0'

Logic '0'

BA16

IO[3]

IO[2]

Fifth

x16:

Cycle

IO[15:8]

IO[7]

IO[1]

IO[0]

First

Logic '0'

WRDA7

WRDA6

WRDA5

WRDA4

WRDA3

WRDA2

WRDA1

WRDA0

Second

Logic '0'

Logic '0'

Logic '0'

Logic '0'

Logic '0'

Logic '0'

WRDA10

WRDA9

WRDA8

Third

Logic '0'

BA7

BA6 / PLA

PA5

PA4

PA3

PA2

PA1

PA0

Fourth

Logic '0'

BA15

BA14

BA13

BA12

BA11

BA10

BA9

BA8

Fifth

Logic '0'

Logic '0'

Logic '0'

Logic '0'

Logic '0'

Logic '0'

Logic '0'

Logic '0'

BA16

Notes:

1.

2.

3.

4.

IO[6]

IO[5]

IO[4]

BYTAx: Byte based Column address, WRDAx: Word based Column address, PAx: Page address, BAx: Block address,

PLA: Plane address

Block address concatenated with page address = actual page address

I/O[15:8] are not used during the addressing sequence and must be driven to Logic ‘0’ (Low)

1st and 2nd address cycles form the column Address, whereas 3rd, 4th and 5th address cycles form the row address

Revision: F

Axia Memory Technology

P a g e 9 | 62

�2Gbit x8, x16: NAND Flash Memory

Table 5: Block Addressing

Block #

Row Address Range

Plane Number

Block 0

000000h ~ 00003Fh

0

Block 1

000040h ~ 00007Fh

1

Block 2

000080h ~ 0000BFh

0

Block 2045

01FF40h ~ 01FF7Fh

1

Block 2046

01FF80h ~ 01FFBFh

0

Block 2047

01FFC0h ~ 01FFFFh

1

……….

Revision: F

Axia Memory Technology

P a g e 10 | 62

�2Gbit x8, x16: NAND Flash Memory

Status Register

Table 6: Status Register Definition

Status Register

Bits

Name

SR[7]

WRPT

SR[6]

RDY

SR[5]

ARDY

SR[4]

ECCS

SR[3]

OTPS

SR[2]

RSVD

SR[1]

PS1

SR[0]

PES

Notes:

1.

2.

3.

4.

5.

6.

7.

Function

Default

State

Description

WP# based Device

Protection

1

0 = Device is protected - WP# is Low

1 = Device Is not protected - WP# is High

Data Cache Register

Ready Status Bit

1

0 = Data Cache is busy - not ready

1 = Data Cache is not busy - ready

Memory Array Ready

Status Bit

Error Correction Code

(ECC) Status

One-Time

Programmable (OTP)

Area Protection Status

Reserved for Future Use

1

0 = Memory Array is busy - not ready

1 = Memory Array is not busy - ready

0 = On-die ECC Engine disabled / Error Count Normal

1 = Page Uncorrectable / Recommend Re-program

0 = OTP Area not protected

1 = OTP Area protected

0

Reserved for Future Use

Program Status of the

Previous Command

Program and Erase

Status of the Current

Command

0

0 = Program was successful

1 = Program was not successful

0 = Program or Erase was successful

1 = Program or Erase was not successful

0

0

0

SR[7] – WRPT: If set to ‘1’, the device is not write protected and can be programmed or erased. If cleared to ‘0’, then the

device is write protected and cannot be programmed or erased. This is always valid regardless of state of the R/B#.

SR[6] - RDY: If set to ‘1’, the device is ready for another command and all other status bits are valid. If cleared to ‘0’, then

the last command issued is not yet complete and all other status bits are not valid. When cache operations are in use, this

bit indicates when the Cache buffer is ready to accept new data. R/B# follows RDY (SR[5] indicates if the last command

was complete).

SR[5] – ARDY: If set to ‘1’, all array operations are complete. If cleared to zero, then there is a command being processed

or an array operation in progress.

SR[4] – ECCS: If the internal ECC is On, this bit indicates if the last read contained ECC errors. It is supported in two modes;

selected using configuration register address 90h bit [4].

a. Mode 1: This mode indicates if a page has a high ECC error count and is recommended to rewrite the page. If set to

‘1’, it is recommended to rewrite the entire page. If cleared to ‘0’, it is in normal state (internal ECC enabled, error

counts are in safe level), or internal ECC disabled.

b. Mode 2: This mode indicates if the page has more ECC errors than the internal engine can correct (UECC). If set to

‘1’, it indicates that the ECC has failed and the page is uncorrectable. If cleared to ‘0’, then it is in normal state (internal

ECC enabled, safely working), or internal ECC disabled.

SR[3] – OTPS: This bit indicates whether the OTP is in protected mode (locked down). This bit is set to ‘1’ if the OTP is

locked down and a program command is issued. It is cleared to ‘0’ when either not in OTP mode, or power-up or when

Reset command is issued.

SR[1] – PS1: This bit is only valid for cache program operations and shows whether the previous operation was a success

or a failure. This bit is not valid until after the second 15h command or the 10h command has been transferred in a Cache

program sequence.

SR[0] – PES: This bit is valid for program and erase operations and shows whether the operation was a success or a failure.

During cache program operations, this bit is only valid when ARDY is set to ‘1’.

Revision: F

Axia Memory Technology

P a g e 11 | 62

�2Gbit x8, x16: NAND Flash Memory

Identification Definition (Address 00h)

Table 7: Device Identification Definition (Address 00h)

Byte

#

0

Bit

7

Bit

6

Bit

5

Bit

4

Bit

3

Bit

2

Bit

1

Bit

0

Values

MID

1

0

1

0

1

1

0

1

ADh

2Gbit, x8, 3.3V

1

1

1

1

0

0

0

1

DAh

2Gbit, x16, 3.3V

1

1

0

0

0

0

0

1

Internal Device # 1

0

0

Internal Device # 2

0

1

CAh

x8/x16

↓

90h/90h

Internal Device # 4

1

0

Internal Device # 8

1

1

0

0

Page Size - 2KB

0

1

Page Size - 4KB

1

0

Page Size - 8KB

Spare Area Size - 8

bytes / 512 bytes

Spare Area Size - 16

bytes / 512 bytes

Block Size - 64KB

1

1

0

0

Block Size - 128KB

0

1

Block Size - 256KB

1

0

Block Size - 512KB

1

1

Options

Manufacturer's ID

1

Device ID

2

Device

Characteristics

3

Array Architecture

Interface Type

Access Time

Revision: F

Cell Type - 2 LEVEL

0

0

Cell Type - 4 LEVEL

0

1

Cell Type - 8 LEVEL

1

0

Cell Type - 16 LEVEL

Simultaneous

Programmed Pages - 1

Simultaneous

Programmed Pages - 2

Simultaneous

Programmed Pages - 4

Simultaneous

Programmed Pages - 8

Interleaved

Programming - Not

Supported

Interleaved

Programming Supported

Cache Program - Not

Supported

Cache Program Supported

Page Size - 1KB

1

1

0

0

0

1

1

0

1

1

0

1

0

1

x8/x16

↓

95h/D5h

0

1

x8

0

x16

1

45ns

0

0

25ns

1

0

Axia Memory Technology

P a g e 12 | 62

�2Gbit x8, x16: NAND Flash Memory

Byte

#

Bit

1

Bit

0

0

0

2-bits per 512 Bytes

0

1

4-bits per 512 Bytes

1

0

8-bits per 512 Bytes

1

1

Options

Reserved for Future

Use

Reserved for Future

Use

1-bit per 512 Bytes

4

ECC Level

Number of Planes

Size of Plane

Reserved

Bit

7

Bit

6

Bit

5

Bit

4

Bit

3

0

1

1

1

Bit

2

1 Plane

0

0

2 Planes

0

1

4 Planes

1

0

8 Planes

1

1

Plane Size - 64Mb

0

0

0

Plane Size - 128Mb

0

0

1

Plane Size - 256Mb

0

1

0

Plane Size - 512Mb

0

1

1

Plane Size - 1Gb

1

0

0

Plane Size - 2Gb

1

0

1

Plane Size - 4Gb

1

1

0

Plane Size - 8Gb

Reserved for Future

Use

1

1

1

Values

x8/x16

↓

46h/46h

0

Identification Definition (Address 20h)

Table 8: Device Identification Definition (Address 20h)

Byte #

Option

Value

0

1

2

3

"O"

"N"

"F"

"I"

4Fh

4Eh

46h

49h

Revision: F

Axia Memory Technology

P a g e 13 | 62

�2Gbit x8, x16: NAND Flash Memory

Parameter Page Structure & Values

Table 9: Parameter Page Structure & Values

Byte #

O/M

Description

Values

Revision Information & Features Block

0-3

M

Signature "O" "N" "F" "I"

4Fh, 4Eh, 46h, 49h

4-5

M

Revision Number

02h, 00h

M

Features Supported

Bit #

Value

0

1 = Supports 16-bit Data bus

1

1 = Supports multiple LUN operations

2

1 = Supports non-sequential page

programming

3

1 = Supports interleaved operations

4

1 = Supports odd to even page

Copyback

5 - 15

0 = Reserved

1Ch, 00h

M

Optional Commands Supported

Bit #

Value

0

1 = Supports Page Cache Program

1

1 = Supports Read Cache

2

1 = Supports Get/Set features

3

1 = Supports Read Status Enhanced

4

1 = Supports Copyback

5

1 = Supports Read Unique ID

6 - 15

0 = Reserved

3Bh, 00h

Reserved (0)

00h, 00h, 00h, 00h,

00h, 00h, 00h, 00h,

00h, 00h, 00h, 00h,

00h, 00h, 00h, 00h,

00h, 00h, 00h, 00h,

00h, 00h

6-7

8-9

10- 31

Manufacturer's Information Block

53h, 4Bh, 20h, 48h,

59h, 4Eh, 49h, 58h,

20h, 20h, 20h, 20h

48h, 32h, 37h, 55h,

32h, 47h, 38h, 46h,

32h, 44h, 4Bh, 41h,

2Dh, 42h, 4Dh, 20h,

20h, 20h, 20h, 20h

32 - 43

M

Manufacturer's ID (12 ASCII Characters)

44 - 63

M

Device Model (20 ASCII Characters)

H27U2G8F2DKA-BM

H27U2G8F2DKA-BM

64

M

JEDEC Manufacturer's ID

ADh

65 - 66

O

Date Code

00h, 00h

00h, 00h, 00h, 00h,

00h, 00h, 00h, 00h,

00h, 00h, 00h, 00h,

00h

67 - 79

Reserved (0)

Memory Organization Block

80 - 83

M

Number of Data Bytes per Page (2048 Bytes)

00h, 08h, 00h, 00h

84 - 85

M

Number of Spare Bytes per Page (128 Bytes)

80h, 00h

86 - 89

M

Number of Data Bytes per Partial Page (512 Bytes)

00h, 00h, 00h, 00h

90 - 91

M

Number of Spare Bytes per Partial Page (16 Bytes)

00h, 00h

92 - 95

M

Number of Pages per Block (64 Pages)

40h, 00h, 00h, 00h

Revision: F

Axia Memory Technology

P a g e 14 | 62

�2Gbit x8, x16: NAND Flash Memory

Byte #

O/M

96 - 99

M

Number of Blocks per Logical Unit (LUN) (2048)

00h, 08h, 00h, 00h

100

M

Number of Logical Units (LUNs)

01h

101

M

Number of address cycles

Bit #

Value

0-3

Row Address Cycles

4-7

Column Address Cycles

23h

102

M

Number of Bits per Cell

01h

103 - 104

M

Bad Blocks Number per LUN (40)

28h, 00h

105 - 106

M

Block Endurance (50K)

05h, 04h

107

M

Guaranteed Valid Blocks at Beginning of Target

01h

108 - 109

M

Block Endurance for Guaranteed Valid Blocks

05h, 04h

110

M

Number of Programs per Page

04h

111

M

Partial Programming Attributes

Bit #

Value

0

1 = Partial Page programming has

Constraints

1-3

1 = Reserved (0)

4

1 = Partial Page Layout

5-7

0 = Reserved

00h

112

M

Number of Bits ECC Correctability

04h

M

Number of Interleaved Address Bits

Bit #

Value

0-3

Number of Interleaved Address Bits

4-7

Reserved (0)

01h

M

Interleaved Operation Attributes

Bit #

Value

0

Overlapped / concurrent Interleaving

Support

1

1 = No Block Address Restrictions

2

1 = Program Cache Supported

3

Address Restrictions for Program

Cache

4-7

0 = Reserved

04h

Reserved (0)

00h, 00h, 00h, 00h,

00h, 00h, 00h, 00h,

00h, 00h, 00h, 00h,

00h

113

114

115 - 127

Description

Values

Electrical Parameter Block

128

129 - 130

M

I/O Pin Capacitance (10pF)

0Ah

M

Timing Mode Support

Bit #

Value

0

1 = Supports Timing mode 0

1

1 = Supports Timing mode 1

2

1 = Supports Timing mode 2

3

1 = Supports Timing mode 3

4

1 = Supports Timing mode 4

5

1 = Supports Timing mode 5

6 - 15

0 = Reserved

1Fh, 00h

Revision: F

Axia Memory Technology

P a g e 15 | 62

�2Gbit x8, x16: NAND Flash Memory

Byte #

O/M

Description

Values

131 - 132

M

Program Cache Timing Mode Support

Bit #

Value

0

1 = Supports Timing mode 0

1

1 = Supports Timing mode 1

2

1 = Supports Timing mode 2

3

1 = Supports Timing mode 3

4

1 = Supports Timing mode 4

5

1 = Supports Timing mode 5

6 - 15

0 = Reserved

133 - 134

M

tPROG Maximum Page Program Time (700 μs)

BCh, 02h

135 - 136

M

tBERS Maximum Block Erase Time (10000 μs)

10h, 27h

137 - 138

M

tR Maximum Page Read Time (25 μs)

1Eh, 00h

Reserved (0)

3Ch, 00h, 00h, 00h,

00h, 00h, 00h, 00h,

00h, 00h, 00h, 00h,

00h, 00h, 00h, 00h,

00h, 00h, 00h, 00h,

00h, 00h, 00h, 00h,

00h

139 - 163

1Fh, 00h

Vendor Block

164 - 165

M

166 - 253

Vendor Specific Revision Number

Vendor Specific

00h, 00h

00h, 00h, 00h, 00h,

00h, 00h, 00h, 00h,

00h, 00h, 00h, 00h,

00h, 00h, 00h, 00h,

00h, 00h, 00h, 00h,

00h, 00h, 00h, 00h,

00h, 00h, 00h, 00h,

00h, 00h, 00h, 00h,

00h, 00h, 00h, 00h,

00h, 00h, 00h, 00h,

00h, 00h, 00h, 00h,

00h, 00h, 00h, 00h,

00h, 00h, 00h, 00h,

00h, 00h, 00h, 00h,

00h, 00h, 00h, 00h,

00h, 00h, 00h, 00h,

00h, 00h, 00h, 00h,

00h, 00h, 00h, 00h,

00h, 00h, 00h, 00h,

00h, 00h, 00h, 00h,

00h, 00h, 00h, 00h,

00h, 00h, 00h

CCh, 92h

254 - 255

M

Integrity CRC

256 - 511

M

Value of Bytes 0 - 255

Not Available

512 - 767

M

Value of Bytes 0 - 255

Not Available

768 +

O

Additional Redundant Parameter Pages

Not Available

Redundant Parameter Pages

Revision: F

Axia Memory Technology

P a g e 16 | 62

�2Gbit x8, x16: NAND Flash Memory

Bus Interface

As mentioned above, the I/O bus on the device is multiplexed. Commands, addresses and data input/output

all share the same I/O pins. Commands and addresses are always supplied on I/O[7:0]. Data uses I/O [7:0]

for x8 configuration and uses I/O[15:0] for x16 configuration.

The read, program or erase command sequences typically consist of a command input cycle, two or five

address input cycles, and one or more data cycles, either input or output.

Table 10: Device Modes Selection

Mode

CE#

CLE

ALE

WE#

RE#

WP#

I/O[x]

Standby

VIH

VIH / VIL

VIH / VIL

VIH / VIL

VIH / VIL

VCC / VSS

VIH / VIL

Command Input

VIL

VIH

VIL

↑

VIH

VIH

Data

Address Input

VIL

VIL

VIH

↑

VIH

VIH

Data

Data Input

VIL

VIL

VIL

↑

VIH

VIH

Data

Data Output

VIL

VIL

VIL

VIH

↓

VIH / VIL

Data

Write Protect

VIH / VIL

VIH / VIL

VIH / VIL

VIH / VIL

VIH / VIL

VIL

VIH / VIL

Notes:

1.

VIH = High (Logic ‘1’), VIL = Low (Logic ‘0’)

Standby

The device enters standby when CE# pin is driven VIH (High). This helps reduce power consumption. In

standby mode, all I/Os are tri-stated (High-Z).

Note: The device enters standby if CE# goes High and the device is not busy (no program/erase operations

in progress).

Busy

The device enters busy when program, erase or read operations are initiated. The device returns to Standby

after the completion of the operation. During busy state, only RESET (FFH) and READ STATUS

REGISTER (70h) commands are accepted by the device.

Table 11: Recommended Signal Selections During Busy

Mode

CE#

CLE

ALE

WE#

RE#

WP#

I/O[x]

Busy Period (READ)

VIH / VIL

VIH / VIL

VIH / VIL

VIH / VIL

VIH / VIL

VIH / VIL

VIH / VIL

Busy Period (Program)

VIH / VIL

VIH / VIL

VIH / VIL

VIH / VIL

VIH / VIL

VIH

VIH / VIL

Busy Period (Erase)

VIH / VIL

VIH / VIL

VIH / VIL

VIH / VIL

VIH / VIL

VIH

VIH / VIL

Notes:

1. VIH = High (Logic ‘1’), VIL = Low (Logic ‘0’)

Device Protection (Write Protect WP#)

The write protect# (WP#) signal enables or disables PROGRAM and ERASE operations within the Flash

device. When WP# is Low, PROGRAM and ERASE operations are disabled. When WP# is High,

PROGRAM and ERASE operations are enabled.

It is recommended that the host drive WP# Low during power-on until VCC is stable to prevent inadvertent

PROGRAM and ERASE operations.

Revision: F

Axia Memory Technology

P a g e 17 | 62

�2Gbit x8, x16: NAND Flash Memory

WP# must be transitioned only when the device is in Standby and prior to beginning a command sequence.

After a command sequence is complete and the device is ready, WP# can be transitioned. After WP# is

transitioned, the host must wait tWW before issuing a new command.

The WP# signal is always an active input, even when CE# is High. This signal should not be multiplexed

with other signals.

Command Input

A command is entered from I/O[7:0] to the command register on the rising edge of WE# when CE# is Low,

ALE is Low, CLE is High, and RE# is High. Most commands are ignored if the device is busy (R/B# = 0);

however, some commands, including READ STATUS (70h), are accepted. For devices with a x16 interface,

I/O[15:8] must be written with zeros when a command is issued.

Figure 4: Command Latch Cycle

CE#

CLE

ALE

Logic

WE#

Logic

RE#

tDS

IOx

tDH

Command

Logic

R/B#

Don t

Care

Address Input

An address is entered to the address register on the rising edge of WE# when CE# is Low, ALE is High,

CLE is Low, and RE# is High. Bits that are not part of the address space must be Low (see Array Addressing

Sequences). The number of address cycles required depends on the command (refer to the command

descriptions to determine addressing requirements). Addresses are input on I/O[7:0] on x8 devices and on

I/O[15:0] on x16 devices. Moreover, for commands that start a modify operation (program/erase), WP#

must be high.

Revision: F

Axia Memory Technology

P a g e 18 | 62

�2Gbit x8, x16: NAND Flash Memory

Figure 5: Address Latch Cycle

CE#

CLE

Logic

ALE

WE#

Logic

RE#

tDS

tDH

Row/Column

Address

IOx

Logic

R/B#

Don t

Care

Data Input

Data is entered to the page buffer (cache register and/or data register) on the rising edge of WE# when

CE# is Low, ALE is Low, CLE is Low, and RE# is High. Data input is ignored if the device is busy (R/B# =

0). Data is input on I/O[7:0] on x8 devices and on I/O[15:0] on x16 devices.

Figure 6: Data Input Cycle

CE#

CLE

ALE

tALS

Logic

tWC

WE#

tWH

tWH

tWP

tWP

Logic

RE#

tDS

IOx

tDH

DIN_M

tDS

tDH

DIN_M+1

tDS

tDH

DIN_M+2

Logic

R/B#

Don t

Care

Revision: F

Axia Memory Technology

P a g e 19 | 62

�2Gbit x8, x16: NAND Flash Memory

Data Output

Data can only be output if the device is not busy and is in the READ state. Data output is supported following

a READ operation from the NAND Flash array. Data is output from the cache register on the falling edge

of RE# when CE# is Low, ALE is Low, CLE is Low, and WE# is High. Data is output on I/O[7:0] on x8

devices and on I/O[15:0] on x16 devices.

Figure 7: Data Output Cycle

tCHZ

CE#

tCOH

CLE

Logic

ALE

Logic

Logic

WE#

tRC

RE#

tRP

tREH

tREA

IOx

High-Z

tREH

tREA

DOUT_M

tRHZ

tREA

DOUT_M+1

DOUT_M+2

tRR

R/B#

Don t

Care

Revision: F

Axia Memory Technology

P a g e 20 | 62

�2Gbit x8, x16: NAND Flash Memory

Command Set

Single Plane Commands

Table 12: Single Plane Command Set

Operation

Command

Cycle

#1

Address

Cycles

Data

Input

Cycles

Command

Cycle

#2

Command

Accepted

Device Busy

0

N/A

Yes

Reset Operation

RESET

FFh

0

Identification Operations

READ ID

90h

1

0

N/A

No

READ UNIQUE ID

EDh

1

0

N/A

No

READ PARAMETER PAGE

ECH

1

0

N/A

No

0

N/A

Yes

Status Register Operation

READ STATUS REGISTER

70h

0

Read Operations

READ MODE

00h

0

0

N/A

No

READ PAGE

READ PAGE CACHE

(Start)

READ PAGE CACHE

(End)

READ PAGE CACHE

(Random)

READ RANDOM DATA

00h

5

0

30h

No

31h

0

0

N/A

No

00h

5

0

31h

No

3Fh

0

0

N/A

No

05h

2

0

E0h

No

Program Operations

PROGRAM PAGE

PROGRAM PAGE CACHE

(End)

PROGRAM PAGE CACHE

(Start)

RANDOM DATA INPUT

80h

4

Yes

10h

No

80h

4

Yes

10h

No

80h

4

Yes

15h

No

85h

2

Yes

N/A

No

Yes

10h

No

No

D0h

No

Re-Program Operations

PROGRAM PAGE 2

(RE-PROGRAM)

8Bh

5

Erase Operation

ERASE BLOCK

60h

3

Data Move Operations (Internal)

READ FOR DATA MOVE

00h

5

No

35h

No

PROGRAM FOR DATA MOVE

85h

5

Optional

10h

No

N/A

No

OTP REGION ENTRY

Revision: F

One-Time Programmable (OTP) Region Operations

29h-17h0

0

04h-19h

Axia Memory Technology

P a g e 21 | 62

�2Gbit x8, x16: NAND Flash Memory

Multi-Plane (MP) / Multi-Device (MD) Commands

Table 13: Multi-Plane / Multi-Device Command Set

CMD

Cycle

#1

Operation

ADDR

Cycles

CMD

Cycle

#2

ADDR

Cycles

CMD

Cycle

#2

ADDR

Cycles

CADB

Program Operations

PROGRAM PAGE MP

80h

80h

5

5

11h - 81h

11h - 80h

5

5

10h

10h

-

No

PROGRAM PAGE CACHE MP (END)

80h

80h

5

5

11h - 81h

11h - 80h

5

5

10h

10h

-

No

PROGRAM PAGE CACHE MP

80h

80h

5

5

11h - 81h

11h - 80h

5

5

15h

15h

-

No

3

3

D0h

D0h

-

No

5

5

10h

10h

-

No

-

-

-

Yes

Erase Operations

60h

60h

ERASE BLOCK MP

3

3

60h

D1h - 60h

Data Move Operations (Internal)

PROGRAM FOR DATA MOVE MP

85h

85h

READ STATUS REGISTER MP/MD

78h

5

5

11h - 81h

11h - 85h

Status Register Operation

3

-

RESET Operation (FFh)

The RESET command (FFh) places the NAND Flash device into the standby mode and aborts any

command sequence in progress. READ, PROGRAM, and ERASE commands can be aborted while the

device is in the busy state using the RESET command. The contents of the memory location being

programmed, or the block being erased are no longer valid - the data may be partially erased or

programmed and is invalid. The command register is cleared and is ready for the next command. The data

register and cache register contents are marked invalid. The status register contains the value E0h when

WP# is High; otherwise it contains the value 60h. R/B# goes Low for tRST during which the device completes

the reset operation.

Revision: F

Axia Memory Technology

P a g e 22 | 62

�2Gbit x8, x16: NAND Flash Memory

Figure 8: RESET Operation

CE#

CLE

ALE

Logic

WE#

Logic

RE#

tDS

IOx

tDH

FFh

tWB

R/B#

READ ID Operation (90h)

The READ ID (90h) command is used to read the product identification information programmed into the

NAND Flash device. This command is accepted when the device is in Standby mode. Writing 90h to the

command register puts the device in read ID mode. The device stays in this mode until another valid

command is issued.

When the 90h command is followed by an 00h address cycle, the device returns a 5-byte identifier code

that includes the manufacturer ID, device configuration, and part-specific information. Reading beyond the

five bytes yields indeterminate data.

When the 90h command is followed by a 20h address cycle, the device returns the 4-byte ONFI identifier

code. Reading beyond the four bytes yields indeterminate data.

Note: Table 7 provides the ID values.

Revision: F

Axia Memory Technology

P a g e 23 | 62

�2Gbit x8, x16: NAND Flash Memory

Figure 9: READ ID Operation

CE#

CLE

tAR

ALE

WE#

tWHR

RE#

tDS

IOx

tDH

90h

tDS

tDH

00h / 20h

Byte 0

Byte 1

Byte 2

Byte 3

Byte 4

READ UNIQUE ID Operation (EDh)

The READ UNIQUE ID (EDh) command is used to read the ONFI Unique identification information

programmed into the NAND Flash device. This command is accepted when the device is in Standby mode.

Writing EDh to the command register puts the device in read UNIQUE ID mode. The device stays in this

mode until another valid command is issued.

When the EDh command is followed by a 00h address cycle, the device returns 16-bytes of a unique value.

The next 16-bytes are the bit-wise complement of the unique value. The host can verify that the Unique ID

was read correctly by performing an XOR of the two values; result should be all ones. The host must monitor

the R/B# pin or wait for the maximum data transfer time (tR) before reading the Unique ID data.

Table 14: Unique ID Data Description

Bytes

0-15

16-31

32-47

48-63

64-79

80-95

96-111

112-127

128-143

144-159

160-175

176-191

192-207

208-223

224-239

240-255

256-271

Revision: F

Information

Unique ID

Unique ID Complement

Unique ID

Unique ID Complement

Unique ID

Unique ID Complement

Unique ID

Unique ID Complement

Unique ID

Unique ID Complement

Unique ID

Unique ID Complement

Unique ID

Unique ID Complement

Unique ID

Unique ID Complement

Unique ID

Axia Memory Technology

P a g e 24 | 62

�2Gbit x8, x16: NAND Flash Memory

Bytes

272-287

288-303

304-319

320-335

336-351

352-367

368-383

384-399

400-415

416-431

432-447

448-463

464-479

480-495

496-511

Information

Unique ID Complement

Unique ID

Unique ID Complement

Unique ID

Unique ID Complement

Unique ID

Unique ID Complement

Unique ID

Unique ID Complement

Unique ID

Unique ID Complement

Unique ID

Unique ID Complement

Unique ID

Unique ID Complement

Figure 10: READ Unique ID Operation

CE#

CLE

ALE

WE#

tWHR

RE#

tDS

IOx

tDH

EDh

tDS

tDH

Unique ID

Byte 0

00h

tWB

Unique ID

Byte 1

Unique ID

Byte 15

tR

R/B#

READ PARAMETER PAGE Operation (ECh)

The READ PARAMETER PAGE (ECh) command is used to read the ONFI parameter page which describes

the device’s organization, features, timings and other behavioral parameters. These values are static and

cannot be altered by the user. The READ PARAMETER PAGE command is accepted by the device when

it is in Standby mode.

Writing ECh to the command register puts the device in read parameter page mode. It stays in this mode

until another valid command is issued. When the ECh command is followed by an 00h address cycle, the

device goes busy for tR. If desired, the RANDOM DATA OUTPUT (05h-E0h) command can be used to

change the location of data output. If the READ STATUS (70h) command is used to monitor for command

completion, the READ MODE (00h) command must be used to re-enable data output mode.

Revision: F

Axia Memory Technology

P a g e 25 | 62

�2Gbit x8, x16: NAND Flash Memory

Figure 11: Parameter Read Operation

CE#

CLE

ALE

WE#

RE#

tDS

IOx

tDH

ECh

tDS

tDH

Param

Byte 0

00h

Param

Byte 1

Param

Byte 255

tR

R/B#

READ STATUS REGISTER Operation (70h)

The device provides its status through its 8-bit status register. After the READ STATUS REGISTER (70h)

command is issued, status register output is enabled. The contents of the status register are returned on

I/O[7:0] for each data output request (toggle RE#).

When the status register output is enabled, changes in the status register are seen on I/O[7:0] as long as

CE# and RE# are Low; it is not necessary to toggle RE# to see the status register update. The command

register remains in Status Read mode until another valid command is issued to it.

Figure 12: Read Status Register Operation

tCEA

CE#

tCLR

CLE

ALE

WE#

RE#

tDS

IOx

tDH

70h

tIR

Status

Output

Don t

Care

Revision: F

Axia Memory Technology

P a g e 26 | 62

�2Gbit x8, x16: NAND Flash Memory

READ MODE Operation (00h)

Upon initial device power up, the device defaults to Read mode. This operation is also initiated by writing

00h and 30h to the command register along with four address cycles. Two types of read operations are

available: random read and serial page read. The random read mode is enabled when the page address is

changed. The repetitive high to low transitions of the RE# clock make the device output the data starting

from the selected column address up to the last column address. The device may output random data in a

page instead of the consecutive sequential data by writing random data output command. Random data

output can be operated multiple times regardless of how many times it is done in a page. Any operation

other than read or random data output causes the device to exit read mode.

The READ MODE (00h) command enables data output and disables status output after a READ operation

(00h-30h, 00-31h) has been modified with a status operation (70h). This command is accepted by the

device when it is ready (RDY = 1, ARDY = 1). It is also accepted by the device during READ PAGE CACHE

(31h, 00h-31h) operations (RDY = 1 and ARDY = 0).

READ PAGE Operation (00h – 30h)

The READ PAGE (00h–30h) command copies a page (x8: 2176 bytes, x16: 1088 words) from the NAND

Flash array to its cache register and enables data output. This command is accepted by the device when it

is ready (RDY = 1, ARDY = 1).

To read a page from the NAND Flash array, the host must first write the 00h command to the command

register, followed by writing 5 address cycles to the address registers, and conclude with writing the 30h

command. The device will go busy (RDY = 0, ARDY = 0) for t R as data is transferred. To determine the

progress of the data transfer, the host can monitor the device’s R/B# signal or use the READ STATUS

REGISTER operation (70h). If the READ STATUS REGISTER operation is used to monitor the progress,

the host must disable status output and enable data output by issuing the READ MODE (00h) command

when the device gets ready (RDY = 1, ARDY = 1).

As mentioned above, two types of read operations are available: random read and serial page read. During

data output the READ RANDOM DATA (05h-E0h) command can be issued if random data output from the

page is desired. Otherwise, the data output is sequential.

Revision: F

Axia Memory Technology

P a g e 27 | 62

�Revision: F

R/B#

IOx

RE#

WE#

ALE

CLE

CE#

tDS

00h

tDH

Column

Address 0

Column

Address 1

tWC

tDH

Row

Address 0

tDS

tDH

Row

Address 1

tDS

tDH

Row

Address 2

tDS

tDS

30h

tDH

tWB

tR

tRR

tAR

tCLR

DOUT 0

tWP

tRC

DOUT 1

DOUT n

tRHZ

tCOH

tCHZ

Don t

Care

2Gbit x8, x16: NAND Flash Memory

Figure 13: Read Page Operation

Axia Memory Technology

P a g e 28 | 62

�2Gbit x8, x16: NAND Flash Memory

Figure 14: Read Page Operation Overview

CB: Page N

Page N To I/Os

DB: Page N

Page N

Memory Array

CMD: 30h

A data transfer operation from the cell array to the Cache

Buffer (CB) via Data Buffer (DB) starts on the rising edge of

WE# in the 30h command input cycle (after the address

information has been latched in). The device will be in the

Busy state during this transfer period.

READ PAGE CACHE Start Operation (31h)

The READ PAGE CACHE Start (31h) command allows reading a page from the cache register while

another page is simultaneously loaded from the Flash array into the data register. A READ PAGE (00h–

30h) command must be issued prior to the READ PAGE CACHE Start command. Operationally, the READ

PAGE CACHE Start (31h) command reads the next sequential page within a block into the data register

(while the previous page is output from the cache register). This command is accepted by the device when

it is ready (RDY = 1, ARDY = 1). It is also accepted during READ PAGE CACHE (31h, 00h-31h) operation

(RDY = 1 and ARDY = 0).

To issue this command, write 31h to the command register. After this command is issued, R/B# goes Low

and the device is busy (RDY = 0, ARDY = 0) for tRBSY. After tRBSY, R/B# goes High (RDY = 1, ARDY = 0),

indicating that the cache register is available and that the specified page is being copied from the NAND

Flash array to the data register. At this point, data can be output from the cache register beginning at column

address 0. The READ RANDOM DATA (05h-E0h) command can be used to change the column address

of the data being output from the cache register.

The READ PAGE CACHE Start (31h) command must not cross block boundaries. The host can enter the

address of the next page to be read from the Flash array. If the host does not enter an address to retrieve,

the next sequential page is read. When no more pages are to be read, the final page is copied into the page

register by issuing the READ PAGE CACHE End (3Fh) command.

Revision: F

Axia Memory Technology

P a g e 29 | 62

�Revision: F

Axia Memory Technology

R/B#

IOx

RE#

WE#

ALE

CLE

CE#

R/B#

IOx

RE#

WE#

ALE

CLE

CE#

tDS

tRCBSY

00h

tDH

tRR

tCLR

Column Address 0

DOUT 0

Column

Address 0

tWP

tRC

Page Address M

Column

Address 1

tWC

DOUT n

tRHW

tDH

Row

Address 0

tDS

tDH

tDS

3Fh

tDH

tDH

tWHR

Row

Address 2

tDS

tWB

Page Address M

Row

Address 1

tDS

tRCBSY

tRR

tCLR

DOUT 0

30h

tDH

Column Address 0

tDS

tWB

tWP

tRC

Page Address M+1

tR

tCHZ

31h

Don t

Care

DOUT n

tRHZ

tCOH

tDS

tDH

tWB

tWHR

tRCBSY

tRR

tCLR

Column Address 0

DOUT 0

tWP

tRC

Page Address M

DOUT n

tRHW

tDS

31h

tDH

2Gbit x8, x16: NAND Flash Memory

Figure 15: Read Page Cache Start Operation

P a g e 30 | 62

�2Gbit x8, x16: NAND Flash Memory

Figure 16: Read Page Cache Start Operation Overview

Page N To I/Os

CB: Page N

CB: Page N+1

DB: Page N

DB: Page N+1

DB: Page N+2

Page N

Page N+1

Page N+2 To I/Os

Page N+1 To I/Os

Cache Buffer

CB: Page N+2

Page N+2

Memory Array

Memory Array

Memory Array

Memory Array

CMD: 30h

CMD: 31h

CMD: 31h

CMD: 3Fh

When 31h command is issued to the device, the data content of the next page is transferred to the Data Buffer (DB) during serial output of the Cache Buffer (CB).

•

•

•

•

•

•

•

During Normal read, Data is transferred from Page N to CB through DB. During this time period, the device outputs Busy state for tR.

After the Ready/Busy returns to Ready, 31h command is issued and data is transferred from DB to CB again. This data transfer takes tRBSY .

Data of Page N+1 is transferred to DB while the data of Page N in CB can be read out by RE# clock simultaneously.

The 31h command makes data of Page N+1 transfer to CB from DB after the completion of the transfer from cell to DB. The devic e outputs Busy state for tRBSY .

Data of Page N+2 is transferred to DB while the data of Page N +1 in CB can be read out by RE# clock simultaneously.

The 3Fh command makes the data of Page N+2 transfer to the CB from the DB after the completion of the transfer to DB. The device outputs Busy state for tRBSY .

Data of Page N+2 in CB can be read out.

READ PAGE CACHE Random Operation (00h - 31h)

The READ PAGE CACHE RANDOM (00h-31h) command allows reading a page from the cache register

while another page is simultaneously loaded from the Flash array into the data register. However, the page

address can be randomly selected (not sequential). A READ PAGE (00h – 30h) command must be issued

prior to the READ PAGE CACHE RANDOM command. This command is accepted by the device when it is

ready (RDY = 1, ARDY = 1). It is also accepted during READ PAGE CACHE (31h, 00h-31h) operation

(RDY = 1 and ARDY = 0).

To issue this command, write 00h to the command register, followed by writing 5 address cycles to the

address register and conclude by writing 31h to the command register. Note that the column address in the

address specified is ignored. After this command is issued, R/B# goes Low and the device is busy (RDY =

0, ARDY = 0) for tRBSY. After tRBSY, R/B# goes High (RDY = 1, ARDY = 0) indicating that the cache register

is available and that the specified page is being copied from the NAND Flash array to the data register.

The data in the cache register can be read beginning at column address 0. The READ RANDOM DATA

(05h-E0h) command can be used to change the column address of the data being output from the cache

register.

Revision: F

Axia Memory Technology

P a g e 31 | 62

�Revision: F

Axia Memory Technology

R/B#

IOx

RE#

WE#

ALE

CLE

CE#

R/B#

IOx

RE#

WE#

ALE

CLE

CE#

tDH

00h

tDH

Page Address N

Row

Address 1

tDS

tDS

tDH

Row

Address 2

tDS

Column

Address 0

tDS

31h

Column

Address 1

tDH

tWB

tWB

tWHR

tRCBSY

Row

Address 0

tRR

tCLR

tWC

tDH

DOUT 0

Column Address 0

tWP

Page Address M

Row

Address 1

tDS

tDH

tRC

Page Address M

Row

Address 2

tDS

DOUT n

tDS

tRHW

30h

tDH

tWB

tDS

3Fh

tR

tDH

tWB

tWHR

tDS

tDH

tRCBSY

00h

tRR

tCLR

Column Address 0

DOUT 0

Column

Address 0

tWP

tRC

Page Address N

Column

Address 1

tWC

tDH

Don t

Care

DOUT n

tRHZ

tCOH

tCHZ

Page Address N

Row

Address 0

tDS

2Gbit x8, x16: NAND Flash Memory

Figure 17: Read Page Cache Random Operation

P a g e 32 | 62

�2Gbit x8, x16: NAND Flash Memory

READ PAGE CACHE End Operation (3Fh)

The READ PAGE CACHE End (3Fh) command ends the read page cache sequence and copies a page

from the data register to the cache register. This command is accepted by the device when it is ready (RDY

= 1, ARDY = 1). It is also accepted by the die (LUN) during READ PAGE CACHE (31h, 00h-31h) operations

(RDY = 1 and ARDY = 0).

To issue the READ PAGE CACHE End (3Fh) command, write 3Fh to the command register. After this

command is issued, R/B# goes LOW and device is busy (RDY = 0, ARDY = 0) for tRBSY. After tRBSY, R/B#

goes HIGH and the device is ready (RDY = 1, ARDY = 1). At this point, data can be output from the cache

register, beginning at column address 0. The READ RANDOM DATA (05h-E0h) command can be used to

change the column address of the data being output from the cache register.

READ RANDOM DATA Operation (05h – E0h)

The READ RANDOM DATA (05h-E0h) command changes the column address of the selected cache

register and enables data output from the device. This command is accepted when the device is ready

(RDY = 1; ARDY = 1) or during CACHE READ operations (RDY = 1; ARDY = 0).

Writing 05h to the command register, followed by two column address cycles containing the column

address, followed by the E0h command, puts the device into data output mode. After the E0h command

cycle is issued, the host must wait at least tWHR before requesting data output. The device stays in data

output mode until another valid command is issued.

Figure 18: Read Random Operation

CE#

CLE

tCLR

ALE

tWC

WE#

tRHW

tWHR

tRC

tWP

RE#

tDS

IOx

DOUT n-1

DOUT n

tDH

05h

tREA

Column

Address 0

Column

Address 1

E0h

tREA

DOUT m

DOUT m+1

DOUT m+k

R/B#

PROGRAM PAGE / PROGRAM PAGE CACHE End Operation (80h – 10h)

As mentioned in the architecture section, programming is page based. Pages must be programmed

sequentially within a block. However, the device also allows multiple partial page programming in a single

page program cycle; Partial page programming of consecutive bytes (1 to 2176) or words (1 to 1088) in a

single page program cycle. The number of consecutive partial page programming operation within the same

page without an intervening erase operation must not exceed 4; for example, 2 times for main array

(1time/512byte) and 2 times for spare array (1time/16byte).

The PROGRAM PAGE (80h-10h) command enables the host to input data to a cache register and program

it to the addressed block and page in the Flash array. This command is accepted by the device when it is

ready (RDY = 1, ARDY = 1). It is also accepted when the device is busy with a PROGRAM PAGE CACHE

(80h-15h) operation (RDY = 1, ARDY = 0). Note that (80h-10h) command is also used to end the program

page cache operation.

Revision: F

Axia Memory Technology

P a g e 33 | 62

�2Gbit x8, x16: NAND Flash Memory

To program an addressed page in the Flash array, write 80h to the command register. Write 5 address

cycles containing the column address and row address. Data input cycles follow. Serial data is input

beginning at the column address specified. At any time during the data input cycle the RANDOM DATA

INPUT command can be issued. When data entry is complete, write 10h to the command register. The

device will go busy (RDY = 0, ARDY = 0) for tPROG as data is programmed.

The internal program state controller automatically executes the algorithms and timings necessary to

program and verify, thereby freeing the system controller for other tasks. To determine the progress of the

data transfer, the host can either monitor the device's R/B# signal or, execute the status operation (70h).

When the device is ready (RDY = 1, ARDY = 1), the host should check the status of the Program/Erase

status (PS1/PES2) bit. The internal program verify detects only errors for "1"s that are not successfully

programmed to "0"s.

Revision: F

Axia Memory Technology

P a g e 34 | 62

�Revision: F

Axia Memory Technology

R/B#

IOx

RE#

WE#

ALE

CLE

CE#

R/B#

IOx

RE#

WE#

ALE

CLE

CE#

80h

DIN m

tDS

tDH

tDS

10h

tDH

Column

Address 0

Column

Address 1

tPRO G

tDH

Row

Address 0

tDS

70h

tWC

tDH

Row

Address 1

tDS

tREA

tDH

Status

Output

Don t

Care

tCOH

Row

Address 2

tDS

tADL

tDS

DIN 0

tDH

2Gbit x8, x16: NAND Flash Memory

Figure 19: Program Page Operation

P a g e 35 | 62

�2Gbit x8, x16: NAND Flash Memory

Figure 20: Program Page Operation Overview

Data Input From I/Os

CB: Data Input

DB: Data Input

Program / Read / Verify

Selected Page

Memory Array

CMD: 10h

The data is programmed from the Data Buffer (DB) to the

selected page on the rising edge of WE# following input of the

h command. After programming, the programmed data is

transferred back to the DB to be automatically verified by the

device. If the programming does not succeed, the Program/

Verify operation is repeated by the device until success is

achieved or until the maximum programming loop count is

reached.

PROGRAM PAGE CACHE Operation (80h – 15h)

PROGRAM PAGE CACHE is used to improve the program throughput by programing data using the cache

register. Cache program is available only within a block. The PROGRAM PAGE CACHE (80h-15h)

command is an extension of the PROGRAM PAGE (80h-10h) command.

The PROGRAM PAGE CACHE (80h-15h) command enables the host to input data to the cache register

while the data register contents are programmed to the memory array. The PROGRAM PAGE CACHE

command is accepted by the device when it is ready (RDY =1, ARDY = 1). It is also accepted by the device

when it is busy with a PROGRAM PAGE CACHE operation (RDY = 1, ARDY = 0).

To input a page to the cache register, write 80h to the command register. Then write 5 address cycles

containing the column address and row address. Data input cycles follow. Serial data is input beginning at

the column address specified. At any time during the data input cycle the RANDOM DATA INPUT (85h)

command can be issued. When data input is complete, write 15h to the command register. The device will

go busy (RDY = 0, ARDY = 0) for tPBSY to copy data from the cache register to the data register, and then

to begin the programming operation.

To determine the progress of the data transfer, the host can either monitor the device's R/B# signal or,

execute the READ STATUS REGISTER (70h) command. When the device is busy with a PROGRAM

PAGE CACHE operation (RDY = 1, ARDY = 0), the host must check the status of the PS1 bit to ensure

cache operation was successful. If, after tPBSY, the host wants to wait for the program cache operation to

complete without issuing PROGRAM PAGE (80h-10h) command, the host should monitor ARDY bit in the

status register until it is 1. The host should then check the status of the PS1 and PES2 bits for program

completion status.

Revision: F

Axia Memory Technology

P a g e 36 | 62

�Revision: F

Axia Memory Technology

R/B#

IOx

RE#

WE#

ALE

CLE

CE#

R/B#

IOx

RE#

WE#

ALE

CLE

CE#

Column

Address 0

tDS

80h

tDH

Column

Address 1

Column

Address 0

Row

Address 0

tWC

Column

Address 1

tDH

Page Address N

Row

Address 1

tDS

Row

Address 0

tDH

tDH

tADL

tDS

tDH

tDH

Row

Address 2

tDS

DIN 0

Page Address M

Row

Address 1

tDS

Row

Address 2

tDS

tWC

tADL

tDS

DIN 0

tDH

DIN m

tDS

10h

tDH

DIN m

tDS

tDH

tPRO G

15h

70h

tCBSY

tREA

tDS

tDH

tCHZ

Don t

Care

tCOH

Status

Output

80h

Column

Address 0

2Gbit x8, x16: NAND Flash Memory

Figure 21: Page Cache Program Operation

P a g e 37 | 62

�Revision: F

Page N

Data Input

From I/Os

•

•

•

•

•

•

CMD: 80h

CMD: 15h

CMD: 80h

Page N+1

CMD: 15h

Memory Array

DB: Data Input M+1

CB:

Page N+1

Data Input

From I/Os

CMD: 80h

Memory Array

Page N+2

CB:

CMD: 10h

Memory Array

DB: Data Input M+2

Program / Read / Verify

The programming with CB is terminated by the 10h command. When the device becomes Ready, it shows that the internal programming of the Page N+2 is completed. The device output busy state from the 10h command until t PROG.

Data for Page N+2 is input to the CB while the data of the Page N+1 is being programmed.

CB: Data Input M+2

DB: Data Input M+1

Program / Read / Verify

Issuing the 15h command, the data in the CB is transferred to the DB after the programming of page N is completed. The device output busy state from the 15h command until t PBSY.

Data is programmed to the selected page while the data for page N+1 is input to the CB.

Data is transferred to the DB by the 15h command. During the transfer the Ready/Busy outputs Busy State (t PBSY).

Data for Page N is input to Cache Buffer (CB).

Issuing the 15h command to the device after serial data input initiates the program operation with Data Buffer (DB). Detailed Program Page Cache Operation steps are as follows:

Memory Array

Page N

DB: Data Input M

Program / Read / Verify

CB: Data Input M+1

Memory Array

DB: Data Input M

DB:

Data Input

From I/Os

Memory Array

CB:

CB: Data Input M

2Gbit x8, x16: NAND Flash Memory

Figure 22: Page Cache Program Operation Overview

Axia Memory Technology

P a g e 38 | 62

�2Gbit x8, x16: NAND Flash Memory

RANDOM DATA INPUT Operation (85h)

The RANDOM DATA INPUT (85h) command changes the column address and enables data input. This

command is accepted by the device when it is ready (RDY = 1; ARDY = 1) or during PROGRAM PAGE

CACHE operations (RDY = 1; ARDY = 0). The RANDOM DATA INPUT (85h) command is allowed after the

required address cycles are specified, but prior to the final program command cycle (10h,15h) of the

following commands while data input is permitted: PROGRAM PAGE (80h-10h), PROGRAM PAGE

CACHE (80h-15h),and PROGRAM FOR DATA MOVE (85h-10h).

Writing 85h to the command register, followed by two column address cycles containing the column

address, puts the device into data input mode. After the second address cycle is issued, the host must wait

at least tADL before inputting data. The device stays in data input mode until another valid command is

issued.

Figure 23: Random data Input Operation

CE#

CLE

ALE

tWC

tADL

WE#

RE#

tDS

IOx

tDH

DIN n-1

tDS

tDH

DIN n

tDS

tDS

tDH

85h

Column

Address 0

Column

Address 1

tDH

DIN m

DIN m+1

Random data Input

DIN m+2

10h

Program Command

R/B#

PROGRAM PAGE 2 (RE-PROGRAM) Operation (8Bh – 10h)

The PROGRAM PAGE 2 (8Bh-10h) command allows re-programming of the same data into a new page if

the last PAGE PROGRAM (80h-10h) operation failed. This command is most efficient if the data to be

programmed is not changed. However, if the data needs to be altered, data in cycles can be initiated before

issuing the program confirm “10h” command.

To re-program the loaded data into a new page address in the Flash array, write 8Bh to the command

register. Write 5 address cycles containing the column address and row address of the new page. Data

input cycles follow. Serial data is input beginning at the column address specified. At any time during the

data input cycle the RANDOM DATA INPUT command can be issued. When data entry is complete, write

10h to the command register. The device will go busy (RDY = 0, ARDY = 0) for tPROG as data is programmed.

To determine the progress of the data transfer, the host can either monitor the device's R/B# signal or,

execute the status operation (70h). When the device is ready (RDY = 1, ARDY = 1), the host should check

the status of the Program/Erase status (PS1/PES2) bits.

Revision: F

Axia Memory Technology

P a g e 39 | 62

�Revision: F

Axia Memory Technology

R/B#

IOx

RE#

WE#

ALE

CLE

CE#

R/B#

IOx

RE#

WE#

ALE

CLE

CE#

tDS

80h

tPRO G

tDH

Column

Address 0

70h

Column

Address 1

tREA

tDH

FAIL!!

Status

E1h

Row

Address 0

tDS

tWC

tDH

Row

Address 1

tDS

tDS

tDH

8Bh

tDH

Row

Address 2

tDS

tADL

DIN 0

Column

Address 0

tDS

tDH

Column

Address 1

tDH

Row

Address 0

tDS

DIN m

tWC

tDH

10h

Row

Address 1

tDS

tDS

tDH

tDH

Row

Address 2

tDS

tDS

10h

Don t

Care

tDH

2Gbit x8, x16: NAND Flash Memory

Figure 24: Program Page 2 (RE-PROGRAM) Operation

P a g e 40 | 62

�2Gbit x8, x16: NAND Flash Memory

ERASE BLOCK Operation (60h – D0h)

The erase operation in the device is done on a block basis. The ERASE BLOCK (60h-D0h) command

erases the specified block in the NAND Flash array. This command is accepted by the device when it is

ready (RDY = 1, ARDY = 1).

To erase a block, write 60h to the command register. Then write 3 address cycles containing the row

address (the page address is not required). Conclude by writing D0h to the command register. The device

will go busy (RDY = 0, ARDY = 0) for tBERS while the block is erased.

To determine the progress of the data transfer, the host can either monitor the device's R/B# signal or,

execute the READ STATUS REGISTER (70h) command. When the device completes an ERASE Block

operation, the host must check the status of the PES2 bit for erase completion status.

Figure 25: Erase Block Operation

tCHZ

CE#

tCOH

CLE

ALE

tADL

WE#

RE#

tDH

IOx

60h

tDH

Row

Address 0

tDH

Row

Address 1

tDS

tDH

Row

Address 2

tDS

tDH

D0h